基于FPGA的数字示波器

4 系统测试分析

(1)单次触发扫描测试,观察设计的示波器能否产生扫描电压,并在信号上升沿开始显示波形。观察结果能够产生扫描电压,并显示波形。

(2)经测量得到输入短路时输出噪声的峰-峰值为1.72 mV。

(3)100 kHz方波校准信号的电压幅值为0.308 V,误差为0.69%。

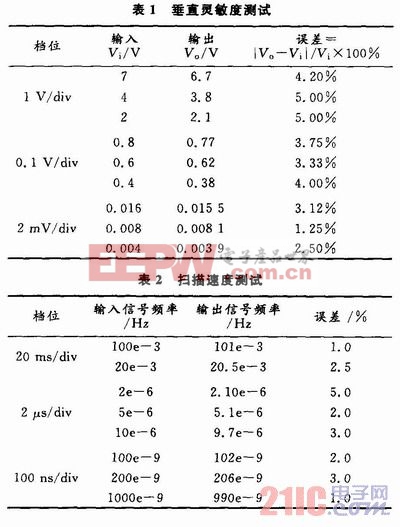

(4)垂直灵敏度测试。正弦信号频率为10 kHz,记录数据如表1所示。

由表2中数据可知,测量结果都在测量误差允许范围内,很好地完成了设计任务。

5 结语

该系统的突出特点采用FPGA作为核心控制器,同时结合NIOS软核的优势,实现了数字示波器的设计。结果表明,系统总体功能完善,集成度高,全数字化,体积小,重量轻,可靠性高,易于程控,使用灵活。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码