基于FPGA的24×24位低功耗乘法器的设计

O 引言

乘法器被广泛应用于各种数字电路系统中,如DSP、数字图像处理等系统。随着便携电予设备的普及,系统的集成度越来越高,这也对产品的功耗及芯片的散热提出了更高的要求。本文提出了一种新的编码算法,通过这种算法实现的乘法器可以进一步降低功耗,从而降低整个电子系统的功耗。

1 乘法器结构

本文介绍的24×24位乘法器的基本结构如图1所示。其中,“降低乘数中‘1’的数量”实现对乘数y的编码,以降低乘数y中“1”的数量,这可以在“部分积产生电路”中降低部分积的数量,“部分积产生电路”产生的部分积在“改进后的阵列加法器”和“超前进位加法器”中相加,最后得到乘积z。

2 降低部分积数量的编码算法

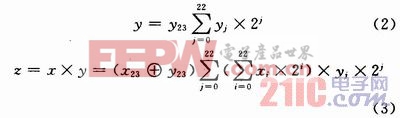

设x,y是被乘数和乘数,它们分别用24位二进制数表示,最高位是符号位,z是乘积,用47位二进制表示,最高位是符号位,“1”表示负数,“0”表示正数。则它们的关系可以用下式表示:

![]()

式中:xi,yi分别是x,y的权位。如果按式(3)进行乘法计算,需要将![]() 与所有的yi相乘,产生23行部分积,然后再将其相加,即使yi=0,也要进行上述运算,这样就势必增加乘法器的功耗和延时,因此,在下面将会对全加器和半加器进行改进,使

与所有的yi相乘,产生23行部分积,然后再将其相加,即使yi=0,也要进行上述运算,这样就势必增加乘法器的功耗和延时,因此,在下面将会对全加器和半加器进行改进,使![]() 仅与yi=1相乘,从而避免与yi=0相乘。首先介绍降低乘数y中“1”的数量的编码算法。用一个事例说明本文介绍的算法的优越性。设m1,m2分别是乘数和被乘数,且令m1=01110111,如果用m2与m1中的每一位相乘,则会产生6个m2和2个“0”列,如果按照Sanjiv Kumar Mangal和 R. M. Patrikar所建议的方法,则:

仅与yi=1相乘,从而避免与yi=0相乘。首先介绍降低乘数y中“1”的数量的编码算法。用一个事例说明本文介绍的算法的优越性。设m1,m2分别是乘数和被乘数,且令m1=01110111,如果用m2与m1中的每一位相乘,则会产生6个m2和2个“0”列,如果按照Sanjiv Kumar Mangal和 R. M. Patrikar所建议的方法,则:

01110111(m1)=10001000(n1)-00010001(n2) (4)

将m2分别与n1和n2相乘,再将它们的乘积相减即得乘积结果。但是,在这一过程中,一共产生4个m2。如果按照本文所建议的方法,会进一步降低m2的数量,即:

01110111(m1)=10000000(n1)-00001001(n2) (5)

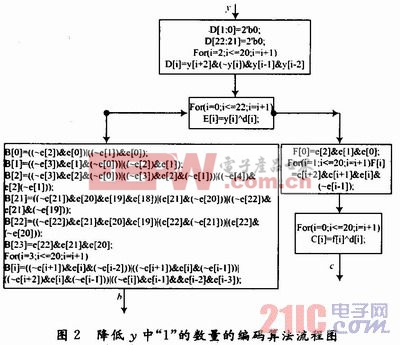

由式(5)可以看出,n1和n2中共有3个“1”,因此,可以进一步降低部分积的数量。当乘数的位数较大时,本文提出的算法优越性更大。具体编码流程如图2所示。

3 部分积的产生及相加

在数字电路中,功耗主要由3部分构成,即:

![]()

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码