基于FPGA的带CRC校验的异步串口通信

1.2.1 波特率设置

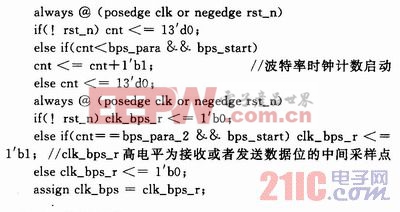

系统时钟是由PFGA的16引脚输入的24 MHz时钟,而异步串口通信的波特率设置为9 600 b/s,所以需要对主频进行分频。分频过程定义了2个常量,分别用来存储波特率96 000 b/s的分频计数最大值bpspara和分频计数的一半bps_para_2。每个系统时钟的上升沿来临时计数器cnt加1,每bps_para_2个系统时钟周期clk_bps改变1次状态,这样就产生了96 000 b/s的波特率。部分分频代码如下:

1.2.2 数据接收

数据接收模块所要完成的任务包括:

(1)连续接收3个字节:1个字节的数据信息和2个字节的数据信息的CRC校验码;

(2)取出这3个字节的第一个字节,重新生成CRC码;

(3)讲新生成的CRC码与接收到得CRC比较,若相同则传输过程中没有出现错误;若不相同则传输过程有错误,等待接收下一组数据。

①单字节串/并转换

串口通信发送数据的格式:1位起始位(低),8位数据位,1位停止位(高),共10位(这里没有校验位ParityBit)传输时的顺序是:起始位+数据位低位---数据位高位+停止位,其时序图如图3所示;

②3字节连续接收并储存

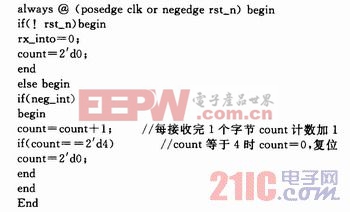

为了连续接收3个字节数据,定义中断寄存器neg_int和计数器count,复位时都清零,开始接收数据时rx_int置高,每接受完1个字节,rx_int清零,此时检测rx_int的下降沿,下降沿到来时计数器count加1,直到接收完第3个字节时count的值是3。部分程序如下:

因为HDL是硬件描述语言,所以必须时刻检测是否有起始位到来,需用几个并行的always语句块来处理。在接受完第1个字节后继续检测下降沿,并把接收到的数据暂存到寄存器data中,接收完第2个字节后仍继续检测下降沿,并暂存数据到crc16[15:8],接收完第3个字节继续检测下降沿,暂存数据到crc16[7:O]。等待下面的校验处理。下面用case语句块来暂存数据。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码