高速高精度钟控比较器的设计

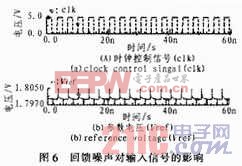

当比较器的时钟频率为300 MHz,输入信号幅度为100 mV时,回馈噪声对比较器基准参考信号产生的尖峰抖动在5 mV以内,如图6所示。与典型的A-B型锁存比较器百毫伏级左右的回馈噪声相比,本文设计的比较器电路结构有较强的抑制回馈噪声的能力。

3 仿真结果

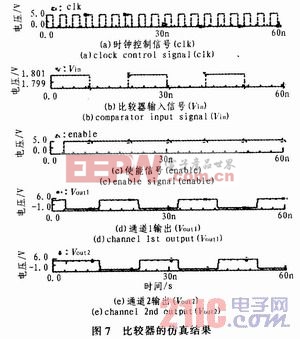

在Cadence软件平台下,用Specte工具对基于TSMC0.18μm CMOS标准工艺模型的比较器电路进行仿真。采用5 V电源电压,300 MHz时钟频率,基准参考电压Vref一直保持为1.8 V,该电路的瞬态响应如图7所示。

第1栏为时钟控制信号clk;第2栏为比较器输入信号Vin,Vin接正负电平为1.801 V和1.799 V的矩形脉冲;第3栏为使能信号enable;第4、5栏为比较器输出节点Vout1和Vout2的波形。图7中曲线表明当enable信号为高电平时,比较器工作并在时钟信号clk下降沿处比较Vin和Vref的大小,在clk上升沿锁存输出结果。当Vin比Vref大1 mV时,输出电压Vout1为低电平,Vout2为高电平,反之输出结果相反。仿真结果符合设计要求,该比较器可达到10位的比较精度。

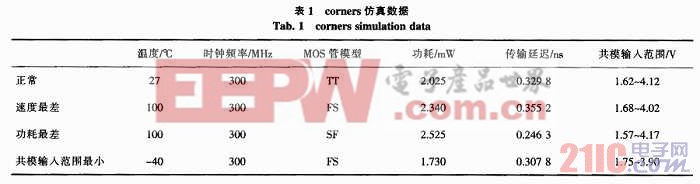

由于工艺及温度变化等因素的影响,实际所得器件参数将产生一定的可变性。为提高产品的成品率及实际性能指标,在27、-40和100℃温度下分别对该电路进行了corners仿真。在不同工艺角下,比较器均可正常工作,其传输延时、功耗和输入共模范围等主要性能参数在一定范围内有所波动,如表1所示。

4 结束语

基于预放大锁存理论,本文设计了一种高速高精度钟控电压比较器。采用预放大级、钟控判断级和输出缓冲级结构实现了高比较速度,获得了较小的可分辨电压。着重分析了改进比较器比较速度和回馈噪声的理论和方法。在TSMC0.18μm CMOS标准工艺下,对可能出现的工艺偏差以及使用温度的变化进行了全面的模拟仿真。仿真结果表明,该钟控比较器在速度、精度、传输延时和回馈噪声等重要性能参数方面有显著的优势,可应用于高速高精度模数转换器与模拟IP核的设计。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码