基于FPGA和硬件描述语言Verilog的液晶显示控制器的设计

本设计是一种基于FPGA(现场可编程门阵列)的液晶显示控制器。与集成电路控制器相比,FPGA更加灵活,可以针对小同的液晶显示模块更改时序信号和显示数据。FPGA的集成度、复杂度和面积优势使得其日益成为一种颇具吸引力的高性价比ASIC替代方案。本文选用Xilinx公司的SpananIII系列XC3S200器件,利用硬件描述语言Verilog设计了液晶显示拧制器,实现了替代专用集成电路驱动控制LCD的作用。

1 功能分析与设计要求

液晶显示模块(LCM)采用深圳拓扑微LM2028、STN图形点阵液晶显示模块,5.7in,320×240点阵,逻辑电压输入为3.0~5.0V,4位控制接口,具有行列驱动电路,白光LED背光源。表l为该液晶显示模块的引脚功能描述。

液晶显示器的扫描方式是逐行扫描,当一行被选通以后,这一行中的各列信号同时加到列上,并维持一个扫描行的时间。这一行维持时间结束后,即选通下一行,同时各列电极也施加下一行的显示电压。

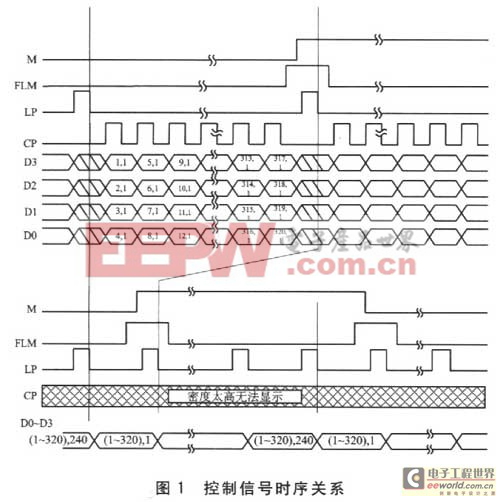

列驱动器逻辑电路由移位寄存器和锁存器构成,在一个显示数据位移脉冲信号CP作用下,将一组显示数据(4位)位移到寄存器中并保持。当下一个CP到来后。移位寄存器中第1位显示数据被移至第2位,这样在80个CP脉冲作用下,一行显示数据被存入寄存器后,寄存器并口对接锁存器,在锁存脉冲LP的作用下,该行数据被锁存到锁存器内输出给列电极。锁存脉冲LP的间隔为一个行周期,而行移位脉冲间隔也为一个行周期,因此二者是一致的。 /Script> 帧扫描信号FLM即为行选通信号,脉宽为一行时间,在行移位脉冲LP作用下,存入移位寄存器后逐行位移,在一帧的最后一行输出高电平,代表下一帧的开始。M为液晶显示交流驱动波形信号,即一帧改变一次波形的极性,防止液晶单方向扭曲变形。更为详细的时序关系如图1所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码