嵌入式单总线控制器设计

2 控制器设计

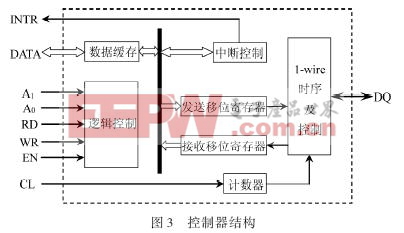

2.1 控制器结构

控制器结构如图3所示,控制器由4部分组成,即逻辑控制、单总线时序控制、数据缓存和计数器。逻辑控制部分用于实现与CPU的通信,D0~D7为8位双向数据线,EN为启动信号,下降沿有效。A1、A0为地址信号,其组合决定控制器的工作状态。A1A0=00,控制器对DS1820执行复位操作;A1A0=01,控制器执行写入操作;A1A0=10,控制器执行读出操作。控制器由外部提供200 kHz的时钟信号CLK,产生5 μs的计数周期,控制器以5 μs为一个时间片形成DS1820的读写时序。计数器的计数输出值控制读写周期。单总线时序控制部分的主要功能是产生单总线的读写时序,并向DS1820输出控制命令,读出DS1820测得的数字温度值及其他输出信息。

2.2 读写时序的实现

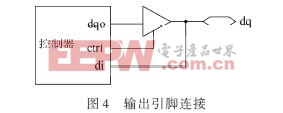

DS1820要求引脚驱动必须是漏极开路引脚,控制器用三态门与DS1820连接,如图4所示。其中ctrl为三态门控制信号,当ctrl=0时输出信号,ctrl=1时输入信号。控制器采用5 μs作为基本计时单位,可以保证DS1820时序关系有一定的余地。

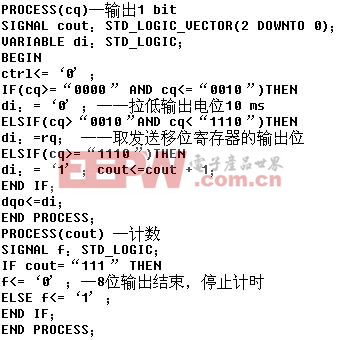

写字节部分VHDL代码:

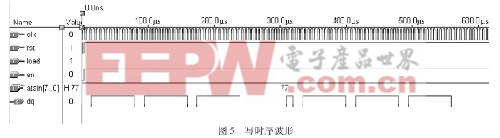

3 仿真波形

控制器的VHDL程序在MAX+plusII平台编译通过,并获得了正确的复位、读、写时序。图5为写时序波形,写入77H字节。每次写入新的bit前,控制器将总线电平拉底10 μs。

基于VHDL的嵌入式DS1820控制器,具有转换速度快、精度高、通用性好等优点。同时,嵌入软核的FPGA可以分担许多微处理器的工作,降低系统对CPU实时性的要求,也降低了软件开发的难度。本文虽然是针对DS1820设计的控制器,但由于单总线通信协议的通用性,也可以用于其他单总线器件。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码