基于FPGA视频采集中的I2C总线设计与实现

由于SAA7111加电复位之后,各寄存器处于不确定状态,因此需要采用I2C总线协议由FPGA作为主方对SAA7111的相关寄存器进行设置。从SAA7111的四个模拟输入端AIll,AI12,AI21,AI22的某一引脚输入的视频图像信号经模拟处理后,一路可通过缓冲器输出到AOUT端用于监视,另一路经A/D转换器后则产生数字色度信号和亮度信号。在分别进行亮度信号处理和色度信号处理后,其亮度信号处理结果的一路将送到色度信号处理器进行综合处理,产生的Y和UV信号经格式化后从VPO(16位)输出;另一路则进入同步分离器,并经数字PLL产生相应的行和场同步信号HS和VS。同时,PLL将驱动时钟发生器,以产生HS锁定的时钟信号LLC和LLC2,SAA7111的所有功能均是在I2C总线控制下完成的。SA-A7111相应的寄存器初始化值见表1。

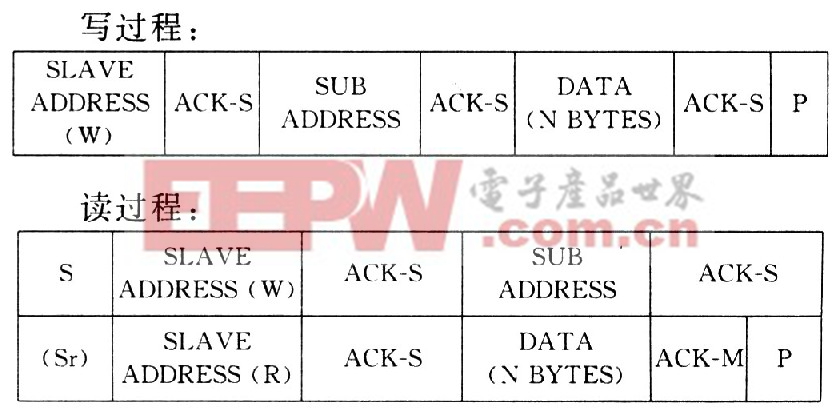

I2C总线控制读/写操作过程如表2、表3所示(S:开始,Sr:重开始,P:停止,-S:从设备,-M:主设备,W:写位,R:读位):

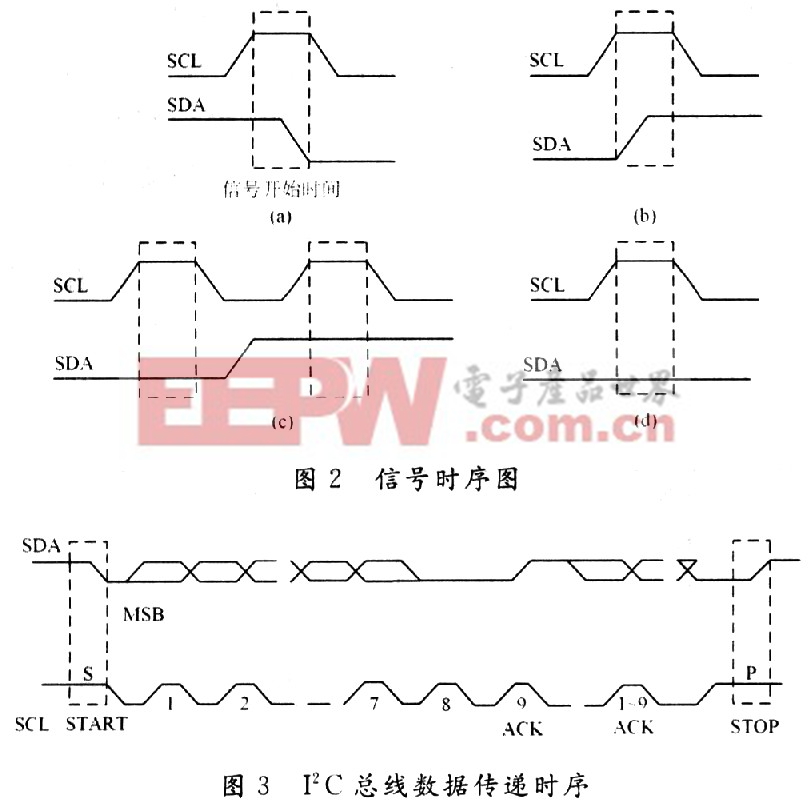

在设计中主要实现以下四种功能:开始条件功能、字节发送功能、应答条件功能和停止条件功能。四种功能信号的时序和数据总线传递如图2、图3所示。

为了完成上述要求和功能,本文采用VHDL语言编写逻辑的方法来模拟I2C总线接口时序逻辑,配置数据可以由主机发送,也可以预先存放,同时用VHDL编写时序逻辑对SAA7111进行初始化配置。根据设计要求,在不同的进程下对串行时钟线(SCL)和串行数据线(SDA)进行设计。时钟信号源采用10 MHz的晶振,分频后作为进程激励信号,基本能够满足SAA7111芯片的数据率要求。但如果在一些更高速的情况下,需要快速通过I2C总线对被控器件进行设置,这里只需将行时钟线(SCL)和串行数据线(SDA)的频率进行修改即可,其接口控制如图4所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码