基于ADC和FPGA脉冲信号测量设计

0引言

测频和测脉宽现在有多种方法。通常基于MCU的信号参数测量,由于其MCU工作频率很低,所以能够达到的精度也比较低,而基于AD10200和FPGA的时域测量精度往往可达10 ns,频率测量精度在100 kHz以内。适应信号的脉宽范围在100 ns~1 ms之间;重复周期在0.05~100ms:频率在0.1 Hz~50 MHz。

AD10200是高速采样芯片,其中内嵌变压器,因此采样电路外部不再需要变压器,使得电路设计更为简单;最低采样速率为105 MSPS,具有3.3 V或者5 V CMOS兼容输出电平,双通道12位采样,补码形式输出,每个通道功耗为0.850W。通常可应用于雷达中频信号接收机、相位组接收机、通信接收机、GPS抗干扰接收机等。

StratixⅡ是Altera公司的中高端主流产品,该产品采用1.2 V、90 nm、9层信号走线,全铜SRAM工艺制造。StratixⅡ内嵌RAM块、DSP块、锁相环(PLL)和外部存储器接口,同时,StratixⅡ也增加了全新的逻辑结构一自适应逻辑模块(ALM),因而增加了动态相位对准(DPA)电路和对新的外部存储器接口的支持。AD芯片可以稳定工作在100 MHz,FPGA速度可高达几百MHz,故可保证系统的测量精度。

1测量原理

1.1时域测量原理

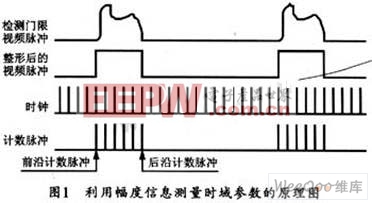

时域测量包括脉宽(PW)测量和脉冲重复周期(Pri)测量,时域测量在FPGA中可利用数字化技术实现。AD的两路输入为两路正交中频信号。经过Cordic算法,即幅相解算之后获得幅度和相位信息,其中利用幅度信息测得时域参数,其原理图如图1所示。

当脉冲信号进入FPGA后,将首先进行门限判定,以将不规则的脉冲信号进行整形并变为规则的脉冲信号。整形后,在脉冲信号上升沿启动脉宽计数器和重复周期计数器,而在该脉冲信号的下降沿锁存脉宽计数器并且在下个脉冲信号上升沿锁存重复周期计数器;由此即可得到脉宽和重复周期的量化值N和M,然后再通过工作时钟的计算,就可得出脉宽和重复周期。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码