基于FPGA的改进型分组交织器的设计与实现

2 改进分组交织器的FPGA设计与实现

2.1 FPGA选取及总体实现

交织器的设计采用Altera公司生产的Cyclone系列FPGA实现。根据系统的总体要求选用了一片EP1C3T100C8芯片,该系列芯片具有成本低、设计灵活、系统便于集成等优点[4],因而在数字通信系统设计中得到了广泛的应用。此外,Cyclone系列芯片内部具有嵌入式RAM存储空间,可以实现较为复杂的逻辑功能,当用作片内存储器时,其存储数据的宽度和深度可由设计人员设定。因而利用存储器可以方便的设计出交织器,从而能够大大减小电路的体积和复杂度。

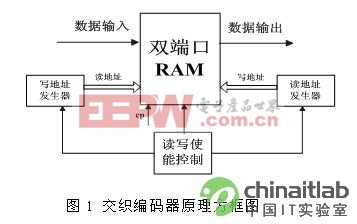

FPGA实现交织器的原理框图如图1所示,从图中可以看出交织器主要由读、写地址序列发生器,双端口RAM以及读写使能控制几部分组成。其中读写使能控制主要用来产生双端口RAM的读写控制信号,并决定读、写地址序列发生器何时启动工作。

FPGA实现交织器的原理框图

2.2 读地址序列产生算法及设计

2.2.1 交织器读地址产生算法

交织器设计的关键部分在于“读/写地址”的产生。设交织器的交织矩阵为n m矩阵,根据分组交织原理,输入数据以0,1,2…,mn-1的顺序地址方式写入存储器,交织后输出为:0,n,2n,…, (m-1)n,1,n+1,2n+1, …,(m-1)n+1,2,…,mn-1.

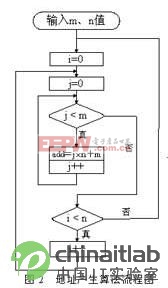

地址产生算法采用双重循环的方式(算法流程如图2所示),算法流程说明如下:

算法流程图

①首先根据信道实际情况及数据帧长,选定合适的交织

将计数变量i,j清零;

②对计数变量j进行判断:如果j<m,则j++;

如果j=m,则跳到第3步;

③对计数变量i进行判断:如果i<n,则i++并将j清零之后跳回第2步;如果i=n,则跳回第1步,开始新一轮循环。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码