多并行处理器接收机设计与实现

摘要:为满足对卫星信号处理越来越快的速.度及通用性的要求,设计并实现了一款高性能的卫星接收机。该接收机的设计在原理上采用多并行处理器的思想,因卫星接收机的中频处理数据量大,实时性高。这样,对芯片的选型提出了很高的要求,通过比较选择了两片目前业界处理能力强的DSP芯片TMS320C6416T核心计算单元,并结合使用了两片功耗低,成本低和大容量的FPGA芯片EP3C120完成卫星接收机中的数据处理,从而使接收机的处理速度和处理能力大大提高,满足了处理高实时性和大数据量卫星信号的要求。

关键词:DSP;FPGA;多并行处理器;卫星接收机

0 引 言

在航空、航天领域,扩频接收机对信号处理速度的要求不断提高。同时,鉴于当前单一处理器导航接收机结构给导航算法带来的约束及并行多处理器技术的日益成熟,为了避免专用卫星接收机的重复研制工作,降低研制的难度、成本和周期,提高可靠性,近几年这一领域中提出了多并行处理器通用接收机硬件平台的思想。基于这一思想,本文的接收机设计在文献[1]的基础上做了一些改进,采用了两片DSP芯片TMS3206416T(以下简称C6416)和两片FPGA芯片EP3C120的设计方案。这样,完成各种不同的信号处理任务可以采用完全统一的硬件平台,所不同的只是该硬件平台上运行的软件。这就增加了系统的灵活性和硬件平台的通用性,并解决了不同信号处理任务分配的问题。

1 接收机板的总体描述

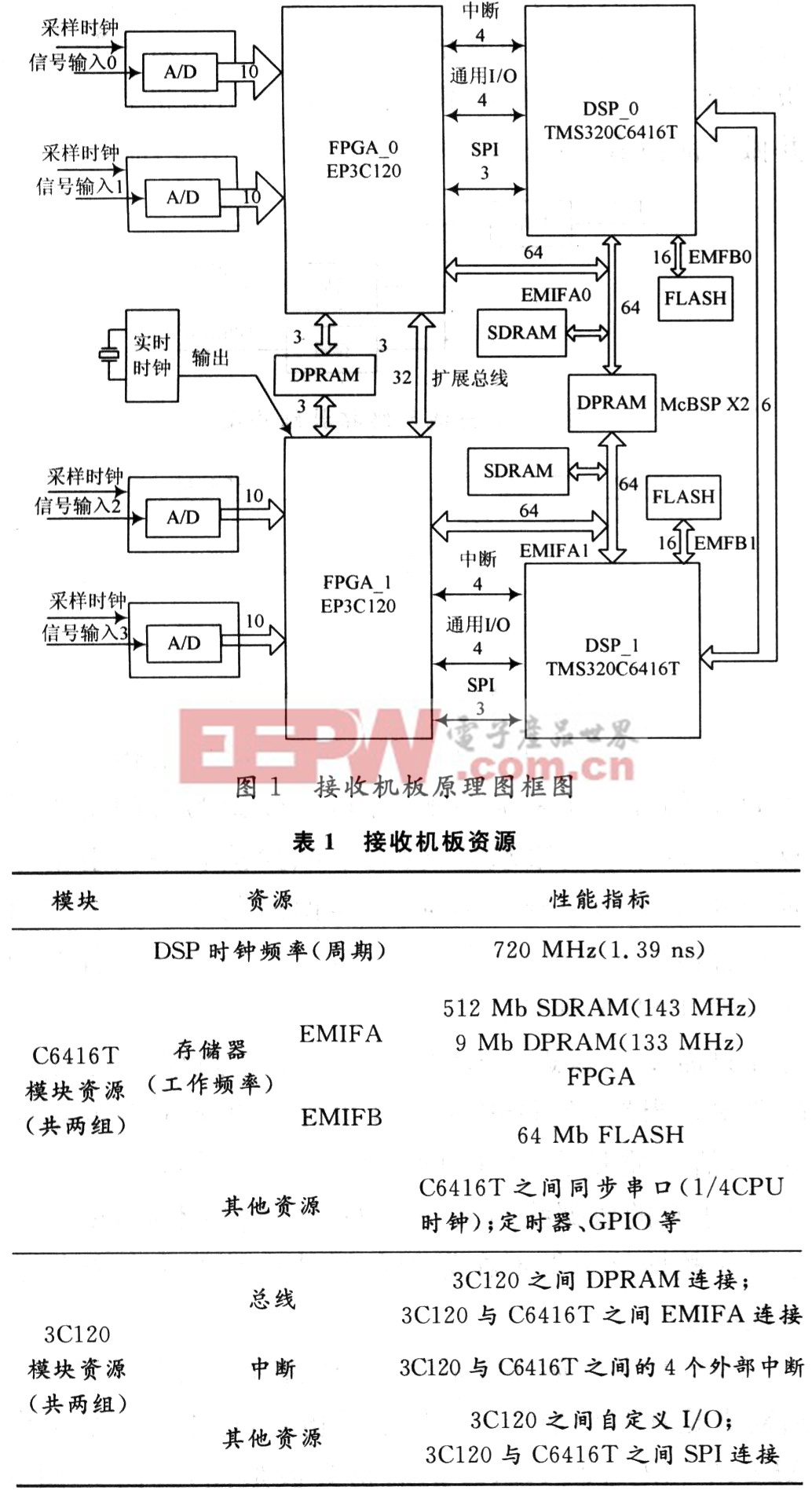

接收机板的原理图框图如图1所示,板上资源及性能指标如表1所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码