半导体封装技术向垂直化方向发展

前瞻性建模

在设计流程的早期使用抽取结果,可使设计人员能够了解拓扑结构和实现选择对系统级行为产生的影响。在了解信号负载、延时、反射和耦合等情况之后,I/O设计人员可实现更加可靠的片上驱动器。类似地,在设计早期使用封装电源面和片上电源栅格电气模型,可使设计人员对封装和芯片之间的去耦电容布置进行权衡,以实现具有最佳性能、最低成本的设计。

利用可行性研究生成的迹线和线绑定长度,设计人员可大致估计信号网络的寄生参数。不过,提取功率传输系统寄生参数需要某种形式(即使近似)的物理实现。不连续的返回路径、电源面的共振以及去耦策略取决于物理实现。因此,在考虑是否分割功率传输面以及它们与信号完整性的交互作用方面,完整的封装提取为做出最终选择提供了很好的支持。这种选择必须在封装设计流程的早期就确定下来;在设计流程后期很难改变,即使提取量仅被用于最终验证,或为同事或客户提供最终设计的电气模型。

TSV封装是一种垂直封装形式,它有望实现更高的集成密度并支持高带宽的存储-逻辑接口。一些看法认为,当仅凭半导体工艺本身无法实现芯片缩放时,TSV封装可作为实现这一目标的手段。

在TSV技术中,是利用硅片上的通孔将裸片堆叠并直接相连,而不是采用线绑定或凸点焊接。尽管工艺技术不断演进,一些方法是先做过孔,而另一些是后做过孔,但都需要高度的协同设计规划,以便在考虑局部片上互连的同时,协调基底间的过孔位置。不过,关键的问题是缺少TSV规划和实现工具,而这会影响该技术获得广泛采用。

堆叠式裸片封装是另一种垂直封装形式,它将若干裸片以堆叠方式集成进单个封装中。与传统封装器件相比,这种形式的高度硅集成极大减小了所需的PCB面积。裸片间的紧密堆叠使该方式成为实现本地化高速、高带宽互连的理想选择,进一步降低了对PCB的要求。与PoP技术相比,堆叠式裸片封装能以更小的体积和重量提供更高的功能密度,但对可靠性和测试的要求必须贯穿在整个设计考虑中。

在开发过程中,堆叠式裸片封装的设计规划至关重要,这极大地影响到最终产品的复杂性和成本。

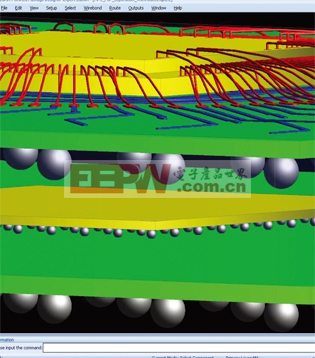

图1:为充分发挥3D半导体封装技术的潜力,需要有针对性的设计规划和分析策略。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码