多路同步串口的FPGA传输实现

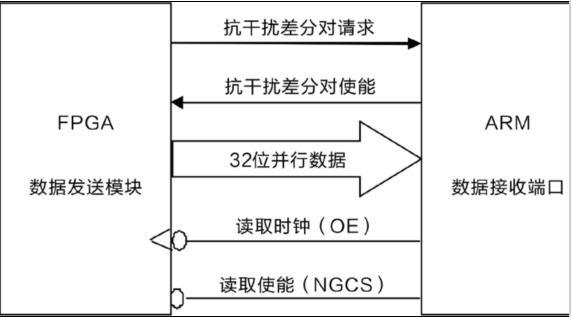

图5 FPGA和ARM的数据传输

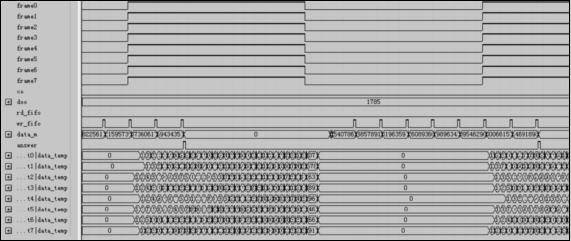

为验证各控制信号的时序逻辑,做如下仿真:FPGA接收及缓存数据。仿真的时序如图6所示。data_temp0~data_temp7 为接收模块的移位寄存器,在frame的下降沿时将数据写入各自的R_FIFO中;R_FIFO中的数据依次通过寄存器data_m写入S_FIFO中。8次写入后,一轮缓存即结束,等待下次请求。

图6 FPGA接收及缓存数据时序仿真图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码