无线基站中的FPGA和DSP组合

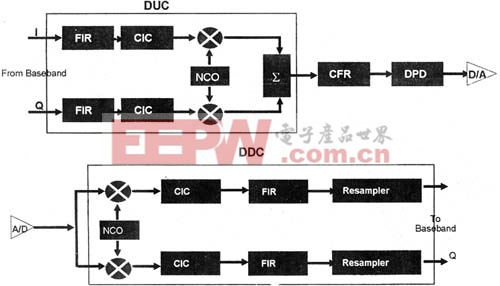

需要CFR和DPD功能来改善用在基站中放大器效率。这些功能也有助于大大降低RF板的总成本。CFR和DPD包含复杂的乘法,取样率可高达100MSPS以上。类似于DUC,在接收端需要数字下变频(DDC)把IF频率变为基频。DUC和DDC都采用复杂的滤波器结构,包括有限脉冲响应(FIR)和级联积分梳状(CIC)滤波器。先进的FPGA提供运行速度高达350MHz的数百个18×18乘法器。这不仅提供并行处理多信道的平台,而且也是一个经济集成单芯片方案。

有效的设计方法

随着标准的稳定,对基站灵活性的要求将降低,而成本变为一个主要的成功因素。选择FPGA将会大大地节省成本。

混合FPGA/DSP基平台,为无线基站提供一种有效的设计方法。产品成功的关键是根据系统吞吐量要求和成本考虑在FPGA和DSP之间进行合理分配。这将保证产品最终不仅仅只是可缩放的和经济的,而且灵活、可配置适合多个标准。(彭京湘)

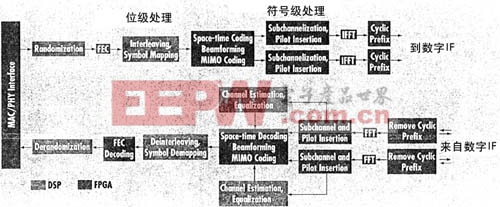

图1 OFDMA系统中DSP/FPGA分配

图2 FPGA中的嵌入式DSP单元

图3 数字RF处理功能

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码