VHDL实现PCM码解调程序模块设计

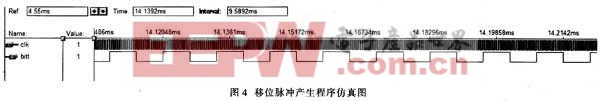

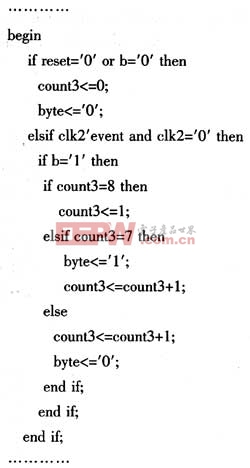

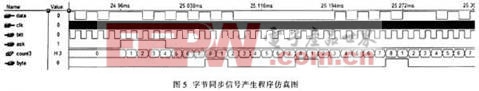

3.2 字节同步信号产生程序

设b为一个标志位,当b为‘1’时,表示检测到请求信号的上升沿且尚未结束一帧传输,该进程的byte为字节同步信号,用来标志一个字节接收完毕。字节同步信号产生程序仿真图如图5所示。

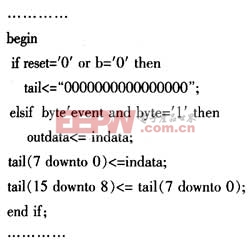

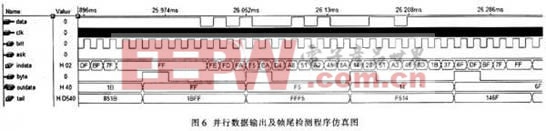

3.3 并行数据输出及帧尾检测程序

并行数据在字节同步信号byte的上升沿输出,outdata为并行数据输出端,同时将并行数据赋值给帧尾标志tail的低8位,将tail的低8位给其高8位,当tail的值为146F时,即表示一帧结束。并行数据输出及帧尾检测程序仿真图见图6。

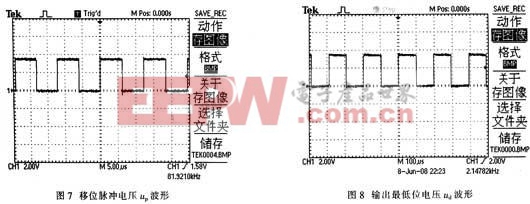

4 调试结果

所发送数据是以00H为起始递增的一串数据,该数据字长200,结尾以146F为标记。调试过程中,南示波器观察波形,可以看到请求信号的频率及脉宽、移位脉冲的频率均符合要求,解调出的并行数据与数据源的数据相吻合。图7和图8分别给出移位脉冲电压up波形和输出最低位电压ud波形。

5 结语

基于FPGA的PCM码解调电路VHDL程序模块设计,可使电路在发出请求脉冲后,在移位脉冲的作用下,同步接收PCM数据,并输出8位并行数据,在帧尾处结束解调。通过仿真及最终电路调试验证了该系统设计能够实现PCM码解调系统功能。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码