抑制鉴相鉴频器中的窄脉冲

本文阐述在鉴相鉴频器(PFD)的反馈通路中加入延迟的重要性,并分析其对电路性能的影响。

本系列上一篇文章介绍了鉴相鉴频器(PFD)——鉴相鉴频器(PFD)入门。该电路可同时检测两路输入之间的相位差和频率差,并具备较宽的线性相位检测范围。

在设计 PFD 时,在反馈通路中加入适量延迟至关重要。如果不加延迟,设计中快速的反馈环路会在电路多个节点产生过窄脉冲(即侏儒脉冲 /runt pulses)。这一点非常关键,因为由这些窄脉冲驱动的后级电路可能会出现工作异常。

本文将讨论如何通过反馈延迟解决窄脉冲问题。为更全面地说明,我们还会分析反馈延迟对 PFD 工作带来的不利影响。最后,在文章结尾,我们将简要介绍 PFD 的等效状态图,完成对 PFD 的讨论。

PFD 窄脉冲问题

图 1 是一种常见的 PFD 实现结构,它采用两个 D 触发器和一个反馈结构的与门产生复位信号。

图 1 鉴相鉴频器

图 2 为该 PFD 在两路输入(R 和 V)频率相同但存在非零相位差时的典型波形。

图 2 两路输入同频且存在相位差时的 PFD 典型波形

在这种情况下,Dn 端会产生窄脉冲。原因是:当 Dn 变为高电平时,Up 和 Dn 同时为高,触发复位通路中的与门。

Dn 会保持高电平直到触发器被复位。Dn 的高电平脉冲宽度等于与门总延迟加上触发器复位操作延迟。如果复位通路速度过快,脉冲会过窄,导致后级电路无法正常工作。因此,为保证 PFD 正常工作,必须在反馈通路中加入适当延迟。

前面讨论的是 R 和 V 存在非零相位差的情况。图 3 为相位差可忽略时的典型波形。

图 3 R 和 V 脉冲相位对齐时的典型波形

可以看到,此时 Up 和 Dn 两端都会出现侏儒脉冲。由于侏儒脉冲无法有效驱动后级电路,从波形可以得出结论:快速反馈通路会在锁定点附近劣化电路性能。同样,该问题可通过有意增加复位通路延迟、展宽输出脉冲来解决。

值得一提的是,锁定点附近 Up 和 Dn 出现的窄脉冲会在 VCO 控制电压上产生纹波。不过,与其他鉴相器(如乘法型鉴相器)产生的纹波相比,这种纹波能量更低、频谱更宽。这些特性让纹波抑制变得容易得多。

在 PFD 反馈环路中加入延迟的影响

为理解 PFD 反馈通路中的延迟如何影响电路工作,我们分析图 4 中的波形。

图 4 门延迟对 PFD 波形的影响

在时刻 t=t1,检测到 R 输入的上升沿。假设 R 到输出的触发器延迟可忽略,则 Up 在 t1 同时变为高电平。

随后在 t=t2,V 输入出现上升沿。忽略 V 到输出的触发器延迟,Dn 也在 t2 变为高电平。

此时 Up 和 Dn 均为高,触发与门在节点 A 产生复位信号。但复位脉冲变为高电平需要一定时间 —— 即与门的延迟。复位脉冲在 t=t3 变高后,触发器还需要额外时间完成输出复位,这一过程在 t=t4 完成。因此,图中时长 τH 等于与门传输延迟加上触发器复位输入端到输出端的延迟。

图 4 底部的 Up-Dn 波形代表 PFD 的最终输出,由 Up 减去 Dn 得到。该波形显示,在时长 τ=τL+τH 内,最终输出保持低电平。

这里的关键点是:输出被复位后,它们不能立即响应输入上升沿而再次变高。换句话说,τL 不能为零。原因在于,当两路输出在 t4 被复位时,与门需要将节点 A 的复位信号拉低,但受限于与门延迟,这一过程无法立即完成。

此外,当复位脉冲在 t=t5 变低后,触发器需要一段额外时间从复位状态恢复,才能准备检测后续输入上升沿。因此 τL 的最小值等于与门传输延迟加上触发器复位恢复时间。

反馈延迟对 PFD 性能的不利影响

如上所述,图 4 中的 Up-Dn 波形即为 PFD 最终输出 Vout。设 τmin 为 τ 的最小值,T 为输入信号周期(见图 4)。此时 Up-Dn 信号的平均值最大值为:

Vout=Vdd×T(T−τmin)+0×τmin=Vdd×(1−Tτmin) 式 1

从上一篇文章已知,PFD 的增益为:

kd=2πVdd 式 2

将式 1 的平均值除以 PFD 增益,可得到 PFD 能检测的最大相位误差:

Δϕmax=kdVout=2π×(1−Tτmin)=2π−ωR×τmin 式 3

其中 ωR 为输入角频率。

上一篇文章讨论的理想 PFD 输入输出特性线性范围为 –2π 到 +2π。而由于门电路延迟不为零,实际 PFD 无法达到这一范围。式 3 表明,最大可检测相位误差取决于 ωR 和 τmin。

实例:计算含非零门延迟 PFD 的线性范围

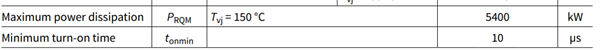

假设某 PFD 所用触发器参数如下:

复位操作延迟:2.5 ns

复位恢复时间:3 ns

与门延迟:1.5 ns

若输入信号频率为 25 MHz,该 PFD 可检测的最大相位误差是多少?

解答

首先计算 τH 和 τL:

τH = 与门延迟 + 触发器复位操作延迟 = 1.5 + 2.5 = 4 ns

τL 最小值 = 与门延迟 + 触发器复位恢复时间 = 1.5 + 3 = 4.5 ns

因此,由非零门延迟导致 Up-Dn 为低的最小时长为:

τmin=τH+τL=4+4.5=8.5 ns

将 ωR=2π×25 MHz 和 τmin=8.5 ns 代入式 3,最大可检测相位误差为:

Δϕmax=2π−2π×25×106×8.5×10−9≈0.79×2π rad 式 4

可见,虽然理想 PFD 可检测的最大相位误差为 2π 弧度,但在给定门延迟下,最大可检测相位误差降至 4.95 弧度,缩减为原来的 0.79 倍。

PFD 的等效状态图

在本系列前文中我们了解到,RS 触发器鉴相器可建模为一个二态器件,其状态图如图 5 所示。

图 5 RS 触发器鉴相器(左)及其等效状态图(右)

PFD 同样可以用状态机建模。粗略分析可知,PFD 等效为至少具有三个独立状态的状态机:

状态 0:Up = 0,Dn = 0

状态 1:Up = 1,Dn = 0

状态 2:Up = 0,Dn = 1

如图 6 所示。

图 6 PFD 电路的状态图

当 PFD 处于状态 0(Up=0,Dn=0)时,R 输入的上升沿会使系统切换到状态 1(Up=1,Dn=0)。电路保持该状态,直到 V 输入的上升沿复位触发器,使系统回到状态 0。

如图 6 所示,V 输入的上升沿会使系统从状态 0 切换到状态 2(Up=0,Dn=1)。电路保持该状态,直到 R 输入的上升沿复位触发器,使系统回到状态 0(Up=0,Dn=0)。

需要注意,上述状态图只是系统的基础模型。如图 4 所示,Up 和 Dn 可能会短暂同时为高。因此,更精确的系统模型应包含第四个状态:Up = 1 且 Dn = 1。

总结

PFD 设计的一个核心要点是防止电路各节点产生过窄脉冲。这些由快速反馈环路产生的侏儒脉冲会导致后级电路工作异常。为确保正常工作,必须在反馈通路中加入合适的延迟。但需要注意,反馈延迟会限制 PFD 的最大可检测相位误差以及最高工作频率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码