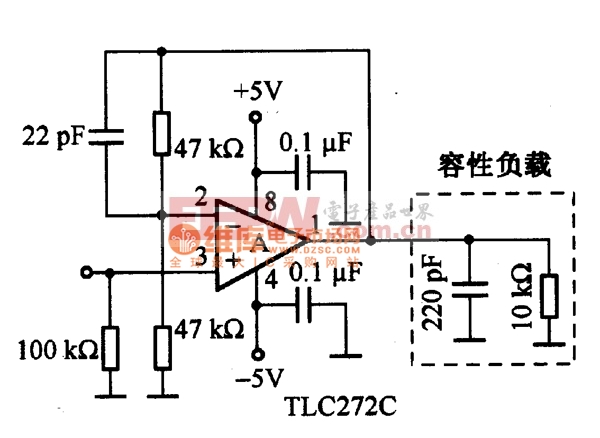

CMOS动放的同相放大电路图

作者:dolphin

时间:2012-07-23

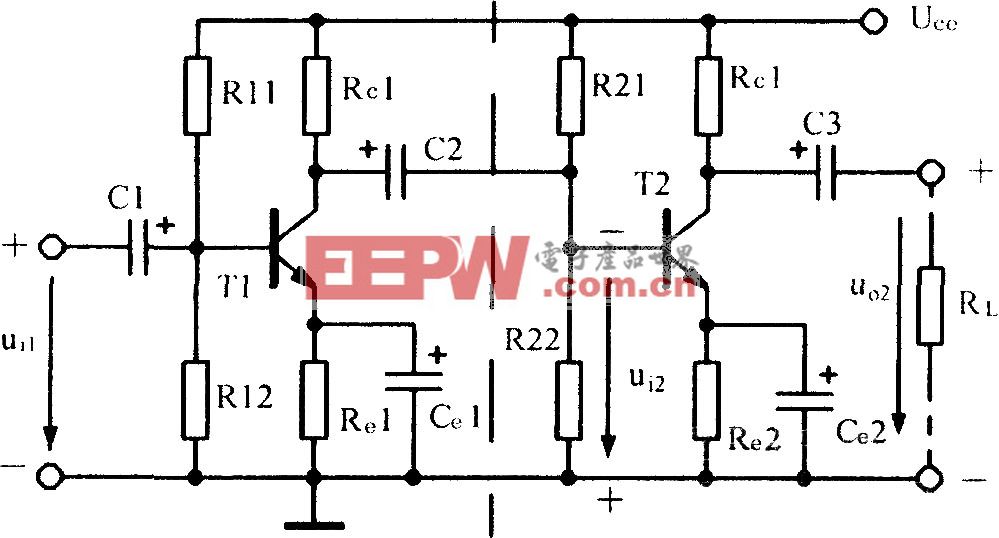

运放输出为容性负载时易产生振荡。运放接容性负载通常有两种情况,一种是印制板的布线与电缆接线的分布电容,另一种是某些电子装置接在运放的输出端,这种电子装置为了消除外部高频信号的影响,在输入与地之间接入较大的电解电容。不同种类的运放对容性负载的承受能力是不同的,常用的CMOS运放对容性负载的承受能力更弱。为此,使用CMOS运放时,在输出端要串联电阻,对容性负载做必要的处理。如图是采用CMOS运放TLC72C的2倍电压增益的同相放大电路。由22OpF电容与1OkΩ打电阻构成容性负载,使电路容易产生振荡。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码