CMOS触发器在CP边沿的工作特性研究

CMOS触发器在CP边沿的工作特性研究

对时钟脉冲(简称CP)边沿时间的要求,是触发器品质评价的重要指标之一。触发器只有在CP边沿陡峭(短的边沿时间)的条件下工作,才能保证其可靠性。文献[1]指出,CMOS电路的基本触发单元是由传输门和或非门组成的主从结构,输入的数据由传输门引导,因此,对时钟脉冲的上升时间和下降时间就有一定的要求。但文献[l]对CMOS触发器在CP边沿的工作模式没有进行深人研究,留下了两个有待探索的问题:一是CP边沿时间过长,触发器会出现什么异常现象及为什么会出现这种现象;二是为保证触发器正常工作,CP边沿时间不能超过多少,它与触发器参数的关系及计算与测量方法。这些问题的回答都依赖于触发器在CP边沿工作特性的研究。为此,采用标准CMOS CD4000系列、高速CMOS 74HC和74HCT系列中有关型号的触发器为实验样品,观察CP边沿时间过长时出现的异常现象,研究异常现象出现的原因,提出CMOS触发器在CP边沿工作的电路模型,探索触发器正常工作时CP边沿时间与触发器参数的关系,从而使文献[1]的有关论述更加具体、深化、正确,这对CMOS触发器的正确使用、研制和提高产品质量都有一定的理论指导意义。

1 CMOS触发器的结构与工作原理

CMOS D触发器足主-从结构形式的一种边沿触发器,CMOS T型触发器、JK触发器、计数单元、移位单元和各种时序电路都由其组成,因此仪以CMOS D触发器为例进行说明。

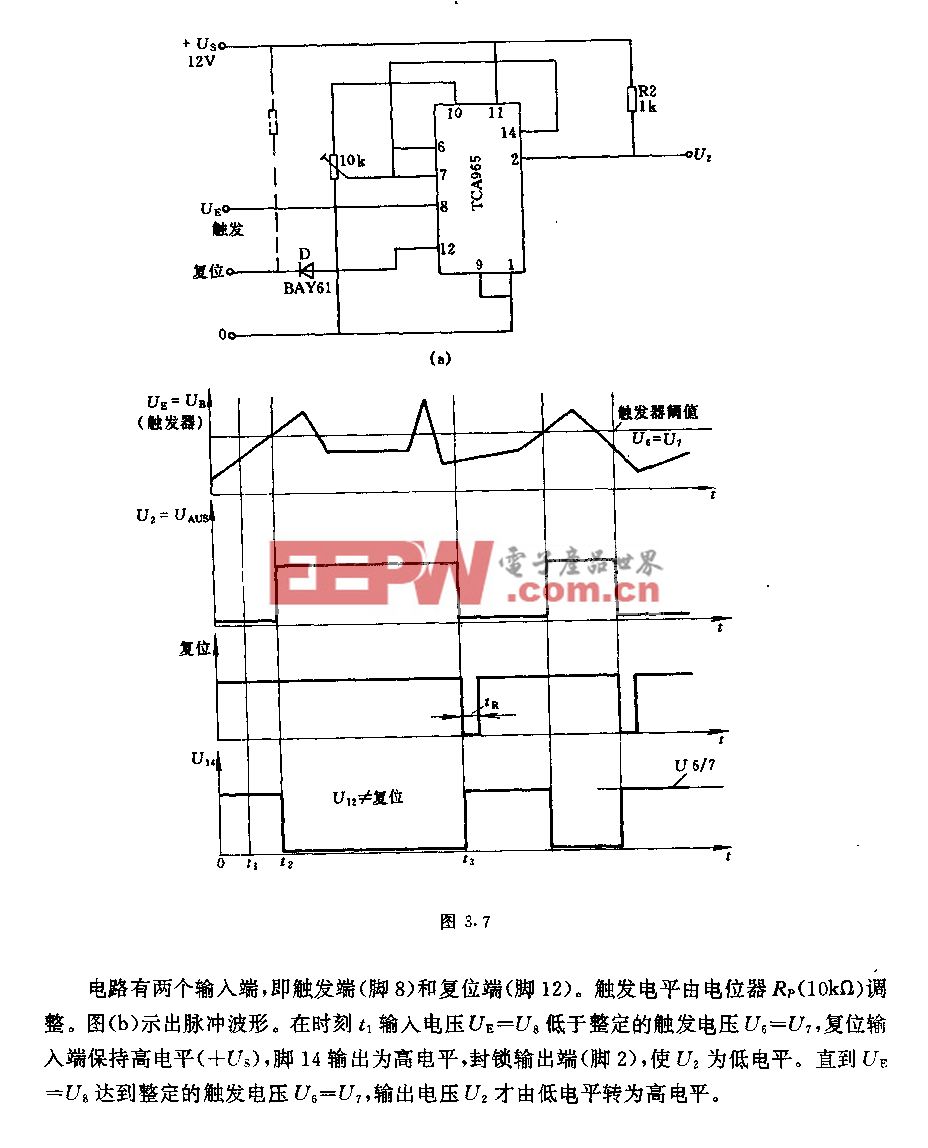

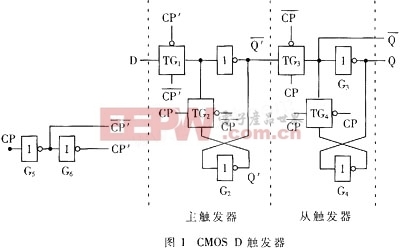

图1是用CMOS传输门和反相器构成的D触发器,反相器G1、G2和传输门TG1、TG2组成了主触发器,反相器G3、G4和传输门TG3、TG4组成了从触发器。TG1和TG3分别为主触发器和从触发器的输入控制门。反相器G5、G6对时钟输入信号CP进行反相及缓冲,其输出CP和CP′作为传输门的控制信号。根据CMOS传输门的工作原理和图中控制信号的极性标注可知,当传输门TG1、TG4导通时,TG2、TG3截止;反之,当TG1、TG4截止时,TG2、TG3导通。

当CP′=0,CP′=1时,TG1导通,TG2截止,D端输入信号送人主触发器中,使Q′=D,Q′=D,但这时主触发器尚未形成反馈连接,不能自行保持。Q′、Q′跟随D端的状态变化;同时,由于TG3截止,TG4导通,所以从触发器形成反馈连接,维持原状态不变,而且它与主触发器的联系被TG3切断。

当CP′的上升沿到达(即CP′跳变为1,CP′下降为0)时,TG1截止,TG2导通,切断了D信号的输入,由于G1的输入电容存储效应,G1输入端电压不会立即消失,于是Q′、Q′在TG1截止前的状态被保存下来;同时由于TG3导通、TG4截止,主触发器的状态通过TG3和G3送到了输出端,使Q=Q′=D(CP上升沿到达时D的状态),而Q=Q′=D。

在CP′=1,CP′=0期间,Q=Q′=D,Q=Q′=D的状态一直不会改变,直到CP′下降沿到达时(即CP′跳变为0,CP′跳变为1),TG2、TG3又截止,TG1、TG4又导通,主触发器又开始接收D端新数据,从触发器维持已转换后的状态。

可见,这种触发器的动作特点是输出端的状态转换发生在CP′的上升沿,而且触发器所保持的状态仅仅取决于CP′上升沿到达时的输入状态。正因为触发器输出端状态的转换发生在CP′的上升沿(即CP的上升沿),所以这是一个CP上升沿触发的边沿触发器,CP上升沿为有效触发沿,或称CP上升沿为有效沿(下降沿为无效沿)。若将四个传输门的控制信号CP′和CP′极性都换成相反的状态,则CP下降沿为有效沿,而上升沿为无效沿。下面以CP上升沿为有效触发沿进行分析。

2 触发器在CP边沿的工作特性研究

2.1 触发器在CP边沿工作状况的实验观察

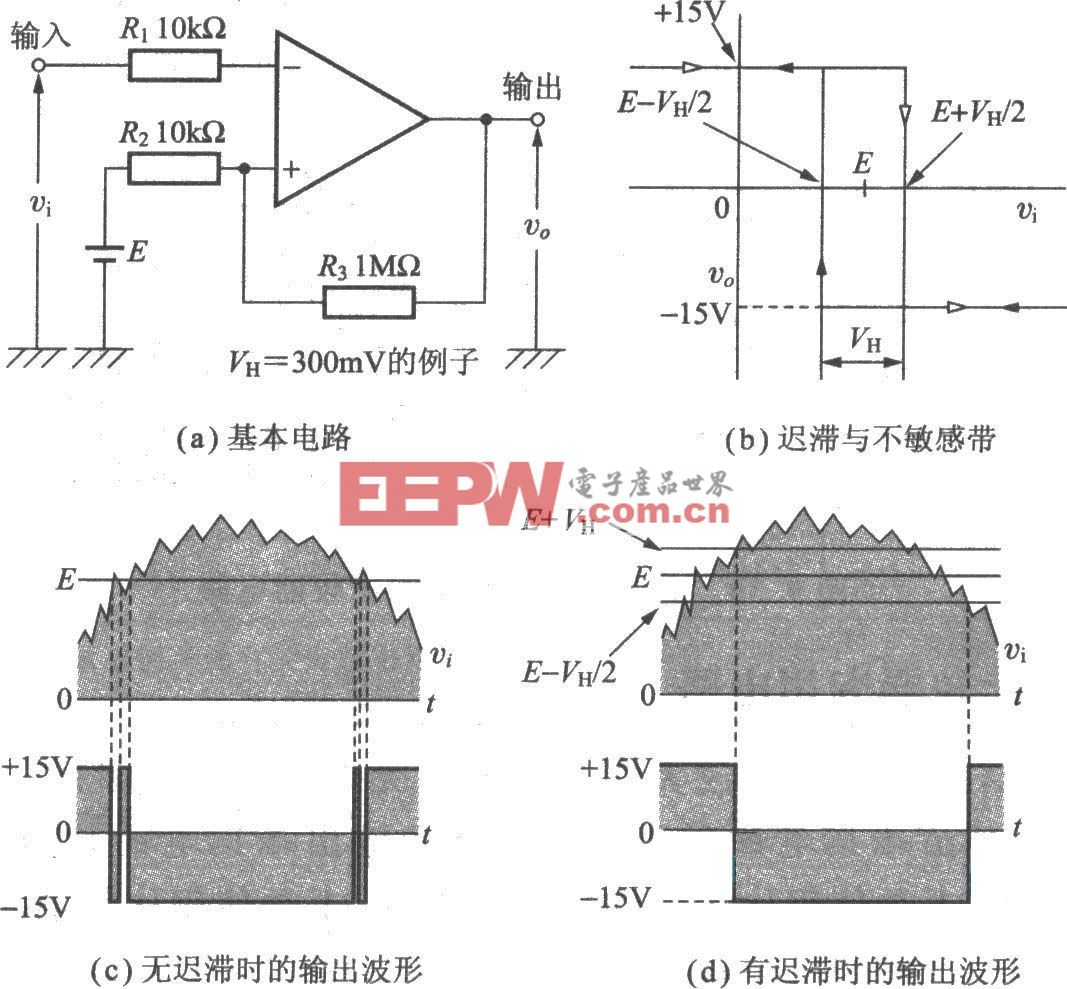

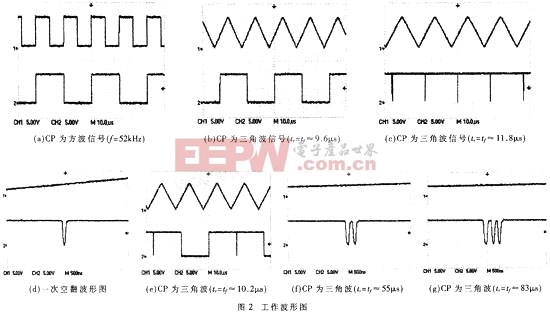

把CMOS D触发器CD4013接成计数工作方式(D端与Q端连接,即D=Q),工作电源电压VDD=10V,由函数发生器DF1641D输出的信号作为时钟端输入信号CP,用数字存储示波器TDS1000(带宽60MHz)同时观察触发器时钟端和输出端波形,如图2所示,称之为工作波形图。

图2(a)所示是CP为频率f=52kHz,幅度Um=10V的方波信号时所观察到的工作波形图(图中上方是CP信号,下方为输出信号,以下同)。由图可见,对应于每一CP信号有效沿(上升沿),输出状态翻转一次,计数工作正常。将上述CP信号转变为同频率的三角波,它的上升沿和下降沿作为CP的上升沿和下降沿,则CP边沿时间tr=tf≈9.6μs,这时工作波形如图2(b)所示,可见输出波形没有发生变化,在对应于CP上升沿某一时刻,输出状态翻转一次。

增大CP上升时间(调节信号频率即可),在tr=tf≈11.8μs时,工作波形如图2(c)所示,输出波形在CP上升沿出现了一次空翻,即从高电平翻转为低电平,又从低电平翻转为高电平的两次翻转。若将示波器时间坐标扩展20倍,该空翻波形如图2(d)所示。

在调节CP上升时间使触发器输出波形由正常计数状态向一次空翻变化时,还出现了图2(e)所示的过渡状态,这是在CP上升时间为tr≈10.2μs瞬间捕捉(采样)到的工作波形图。由图可见,对应于CP第1个和第4个上升沿输出空翻一次,出现异常现象。而对于第2、3、5个CP上升沿,输出只翻转一次,属正常工作状态。

继续增大CP上升时间,对应CP上升沿还会出现图2(f)、图2(g)所示的波形图以及更多次空翻现象,事实上,输出已出现振荡现象。

在对其他CMOS触发器如CD4027(JK触发器)、高速CMOS触发器74HC73(JK触发器)、74HC74(D触发器)、74HC107(JK触发器)和74HCT107(JK触发器)的实验中,也出现了类似的现象。即若CP边沿时间过长,对应于CP有效沿,触发器输出状态会出现振荡现象,一次空翻只是一次振荡而已,而在CP无效沿,输出状态不会出现异常现象。

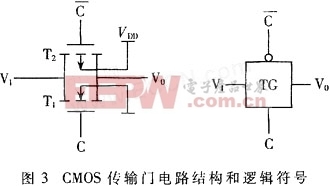

2.2 传输门在CP边沿的共同导通现象

CMOS传输门电路结构如图3所示。它是由增强型NMOS管T1和PMOS管T2的源极和漏极分别相接而成,其连接处就是传输门的输入端V1和输出端V0,PMOS管衬底接工作电源电压VDD,NMOS管衬底接地,电压0伏,加在两管栅极的是一对互补的控制信号C和C,它们的极性变换控制传输门输入端与输出端之间的导通与截止。

通常传输门中NMOS管开启电压VTN和PMOS管的开启电压VTP大小相等,即VTN=|VTP|=VT,且工作电源电压VDDVTN+|VTP|。当C=0,c=1时,NMOS管和PMOS管的栅极和衬底之间电压均为零,源极和漏极之间不存在导电沟道,两管均截止,V1和V0之间是断开的。在C由0开始上升的过程中,当它上升到NMOS管的开启电压VTN时,相应的C则要由高电平VDD下降同样的幅度,即下降为VDD-|VTP|。这时NMOS管和PMOS管均开始导通。所以图1中TG2、TG3在CP′上升到VTN时便会开始导通,尽管TG1、TG4所加的控制信号与TG2、TG3是反相的,但这时它们的NMOS管和PMOS管的栅极对衬底的电压还在开启电压之上(因为VDDVTN+|VTP|),TG1、TG4还是处于导通状态,直到CP′上升到VDD-|VTP|(相应的CP′下降到VTN)时,TG1、TG4才会截止。可见CP′上升过程中,存在TG1、TG4和TG2、TG3共同导通的工作状态,共同导通的时间是CP′由VTN上升到(VDD-|VTP|)所经历的时间。

对CP′下降过程作同样分析可知,在CP′下降过程中,也会出现TG1、TG4和TG2、TG3共同导通的现象,共同导通的时间是CP′从(VDD-|VTP|)下降到VTN所经历的时间。

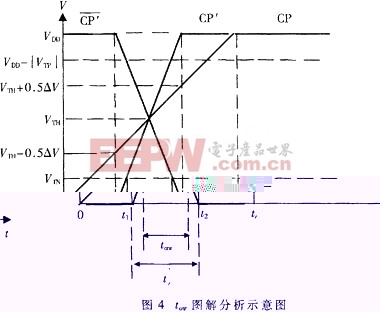

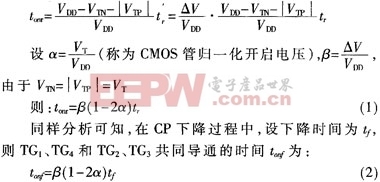

图1中传输门TG1、TG4和TG2、TG3在CP上升时共同导通时间tonr可由图4示意说明。图中CP是触发器时钟端输入信号上升沿波形,设其为线性上升,上升时间为tr。CP′和CP′分别为在CP作用下,G5、G6输出的折线近似波形,VTH是它们的阈值电压,通常近似为电源电压VDD的一半,即VTH≈1/2VDD。设反相器转换区电压大小为△V,由于它们的传输特性在阈值电压处有非常陡峭的变化,所以在CP上升过程中,当它小于(VTH-0.5△V)时,即未进入转换区时,CP′、CP′几乎不变。而CP电压处在转换区内,CP′和CP′均会急剧变化,当CP电压上升到VTH+0.5△V以后,则CP′、CP′又几乎不变。所以图4中曲线CP′和CP′采用了折线近似,它们的转折点分别为CP上升到VTH-0.5△V的t1时刻和上升到VTH+0.5△V的t2时刻,故CP′的下降时间和CP′的上升时间都等于CP在转换区内所经历的时间  。

。

VTH和VTP表示传输门中NMOS管和PMOS管的开启电压,由前面分析可知,CP上升过程中,TG1、TG4和TG2、TG3共同导通的时间是CP′由VTH升到(VDD-|VTP|)所经历的时间,也等于CP′由(VDD-|VTP|)下降到VTN的时间,故共同导通时间为tonr:

2.3 触发器在CP边沿的工作特性

2.3.1 在CP上升沿的工作特性

图1中CP′=0,CP′=1时,TG3断开,TG4导通。若Q′=1,Q=0,则表示反相器G1中的PMOS管导通,而NMOS管截止;反相器G4中的PMOS管截止,NMOS管导通。采用MOS管的开关等效电路,则主、从触发器之间的等效电路如图5所示。图中和Ron(P)是G1中PMOS管的导通电阻,Ron(N)是G4中NMOS管的导通电阻,a、b点分别为G2、G3的输入端,C2、C3是其输入电容,RTG3、RTG4是传输门TG3、TG4的导通电阻,开关K1、k4则表示其工作状态。

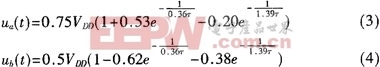

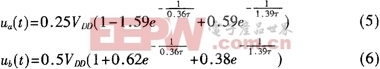

文献[3]表明,触发器最简单的版图布局结构选取所有器件有相同的宽长比W/L,所以Ron(P)≈Ron(N)≈RTG3≈RTG4=R,C2≈C3=C,在CP′上升沿传输门共同导通时间阶段tonr内,主、从触发器间的等效电路如图6所示。这是一个含有两个同类储能元件的二阶电路,固有频率只可能是两个不相等的负实根,电路的响应是欠阻尼的,利用拉普拉斯变换,可以求得a、b两点电压分别为:

式中T=RC是反相器G1~G4中MOS管的导通电阻与输入电容的乘积。

可以画出ua(t)和ub(t)的波形如图7所示。式(3)和图7(a)表明,在tonr期间,门G2的输入电压大于阈值电压,且在逻辑1区,从而通过G2的输出保证G1中PMOS管导通。式(4)和图7(b)表明,G3的输入电压将趋向阈值电压0.5VDD,一旦该电压进入阈值电压附近的转换区范围内,则G3被偏置在放大工作状态,对输入信号起放大作用。目前生产的CD4000系列和74HC系列的CMOS电路都采用带缓冲级的结构,线性增益很高,干扰信号或电路内部的噪声扰动会被放大并经G4又反馈到G3输入端,形成强烈的正反馈过程。因而出现了图2中的异变现象,直到CP′继续上升,传输门的共同导通时间结束,TG4截止(图6中K4断开)时为止。

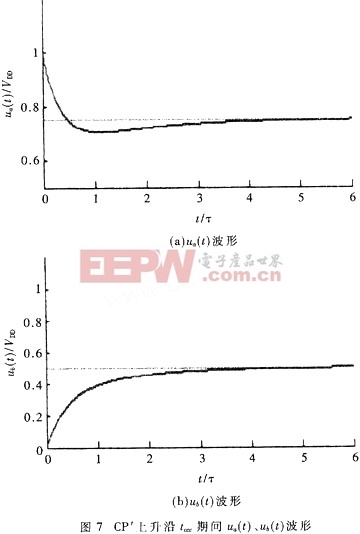

在Q′=0,Q=1的条件下进行同样的分析,可得到类似的结果,这时:

式(5)所表示的G2输入电压小于阈值电压,在逻辑0区,从而通过G2的输出保证G1中NMOS管的导通,使Q′=0;而式(6)所表示的G3输入电压也会趋向阈值电压0.5VDD,使输出出现异变现象。

2.3.2 在CP下降沿的工作特性

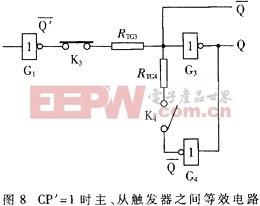

在CP′=1,CP′=0时,TG3导通,TG4截止,主、从触发器之间工作的等效电路如图8所示。这时G4的输出总是等于G3的输入,即截止的传输门TG4输出端与输入端之间的信号相等。所以在CP下降沿,传输门TG4开始导通(图中K4闭合)时,会使G3的输出锁定,而TG3的继续导通对输出不产生影响。这就是说,在CP下降沿,传输门的共同导通状态不会引起触发器输出状态的异常变化。

2.3.3 触发器对CP边沿时间的要求

要使触发器在CP上升沿不出现异变现象,则要求G3的输入电压ub(t)变化到转换区之前,传输门TG4必须截止。测试表明,转换区电压△V=(0.01~0.05)VDD,这就要求ub(t)变化到稳态值0.5VDD的95%~99%之前,传输门共同导通时间结束,TG4截止。在式(4)ub(t)表达式中,第二项指数函数的时间常数比第三项小得多,故在ub(t)趋向转换区时,其变化规律主要由第三项指数函数的时剧常数1.39T决定。所以要求传输门的共同导通时间tonr为:

本实验测得tr应小于010.2μs,理论计算与实验测试取得了比较吻合的结果。

对于有效触发沿是CP下降沿的CNOS触发器,同样分析可得要求CP下降时间tf为:

3 结论与说明

(1) CMOS触发器在CP边沿会出现传输门共同导通的工作状态,这种工作状态会导致触发器在CP有效触发沿产生输出状态振荡的异变现象。

(2) 为了使触发器在CP触发沿不产生异变现象,保证其正常的工作状态,应对CP触发沿提出时间要求,它除与器件自身参数有关外,还与工作电源电压VDD有关,式(8)、式(9)表明了这种关系。

(3) 触发器在CP信号无效触发沿不会出现输出状态的异变现象,从这个角度讲,对CP信号无效触发沿不存在时间要求,但CP边沿时间大,电路的功耗也大,所以也应同样加以限制。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码