CD4046引脚图资料

CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

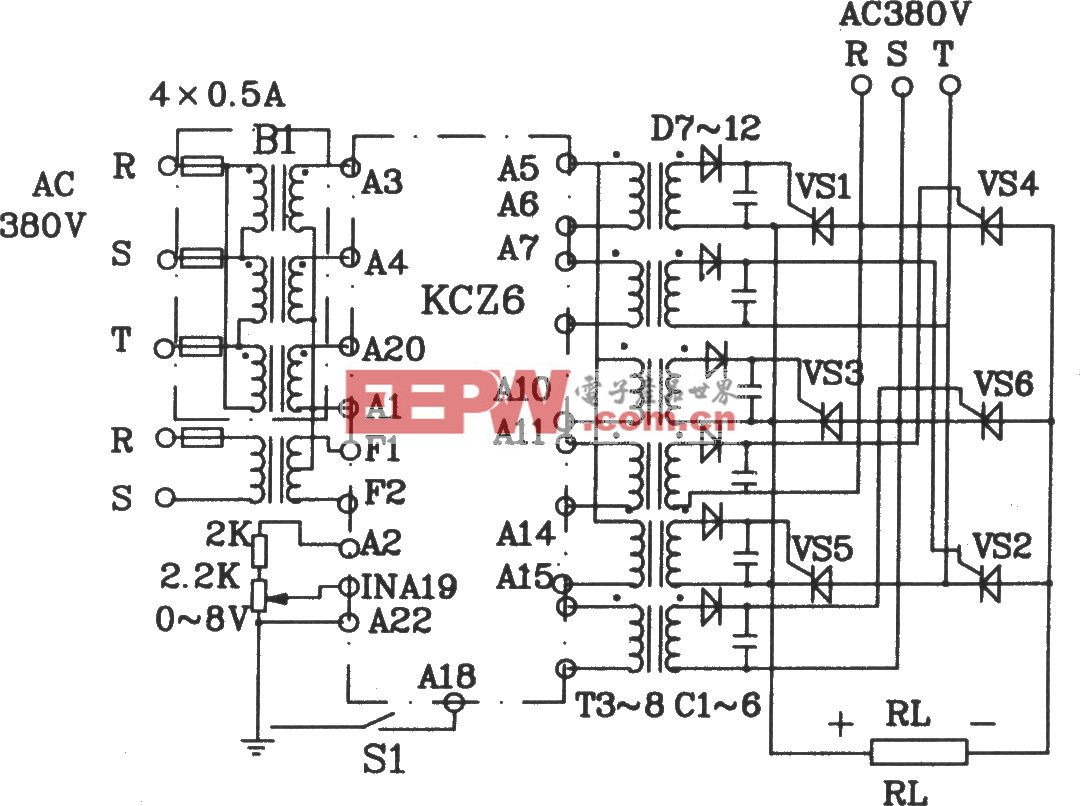

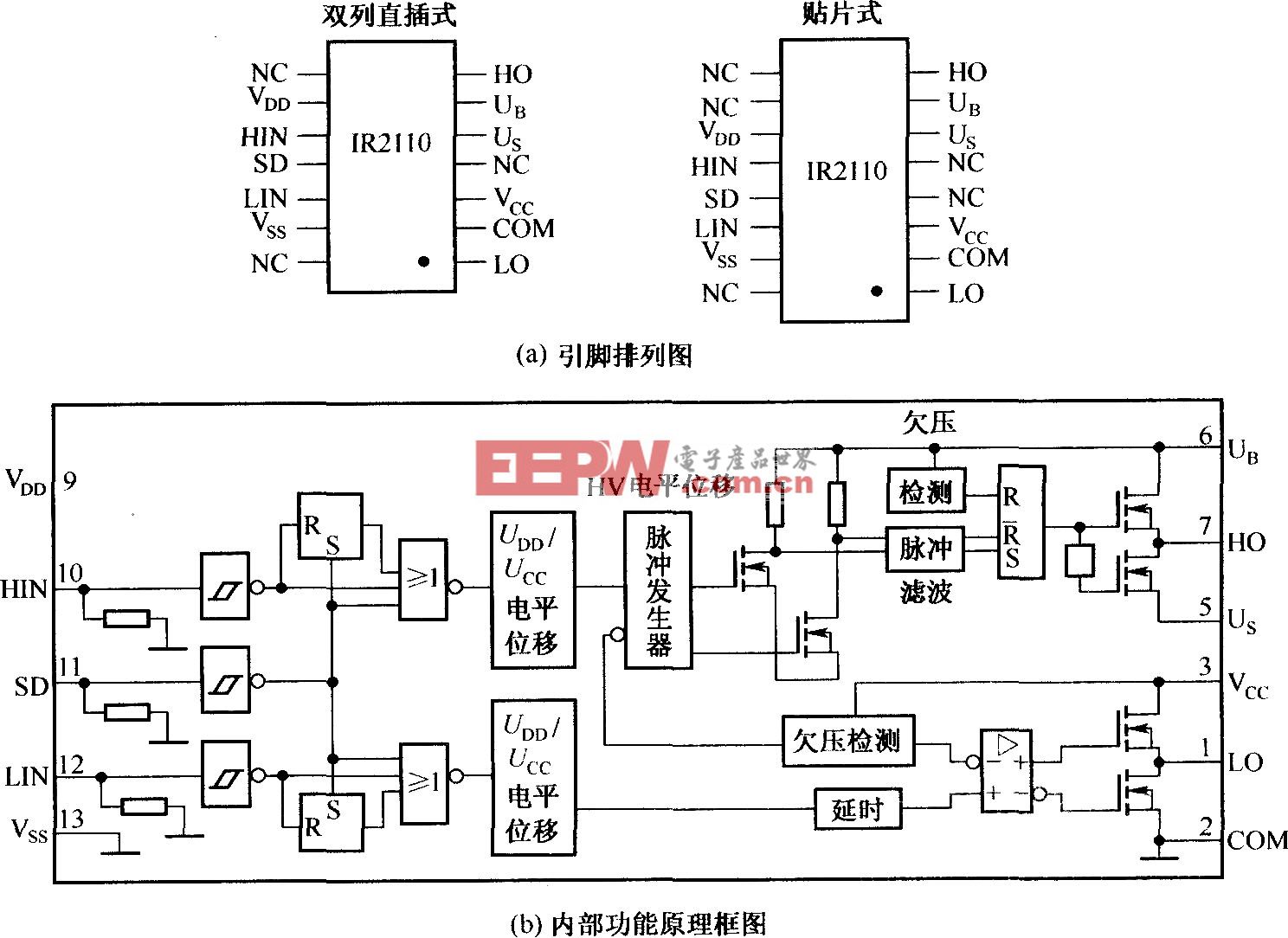

CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。锁相环主要由相位比较器(PC)、压控振荡器(VCO)。低通滤波器三部分组成,如下所示。

CD4046内部电原理框图

CD4046工作原理:输入信号 Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,图3开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f2迅速逼近信号频率f1。VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。若开关K拨至13脚,则相位比较器Ⅱ工作,过程与上述相同,不再赘述。

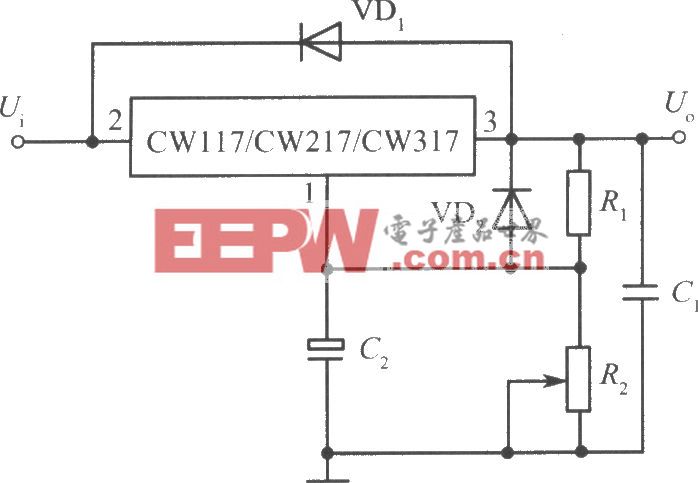

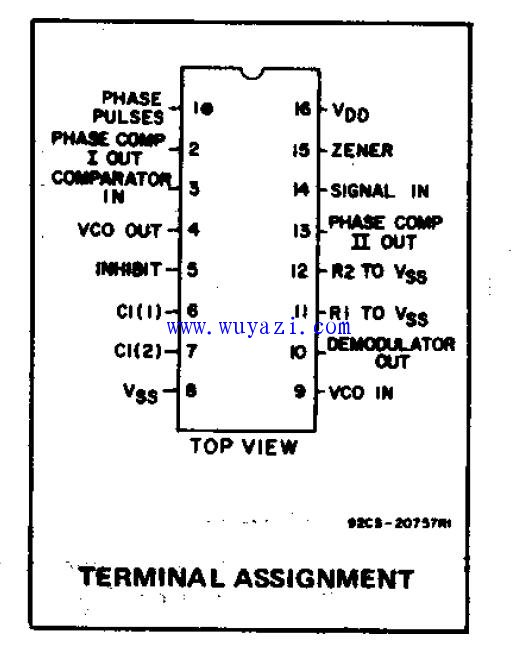

下图是CD4046的引脚排列,采用16脚双列直插式,各管脚功能:

1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

CD4046引脚图

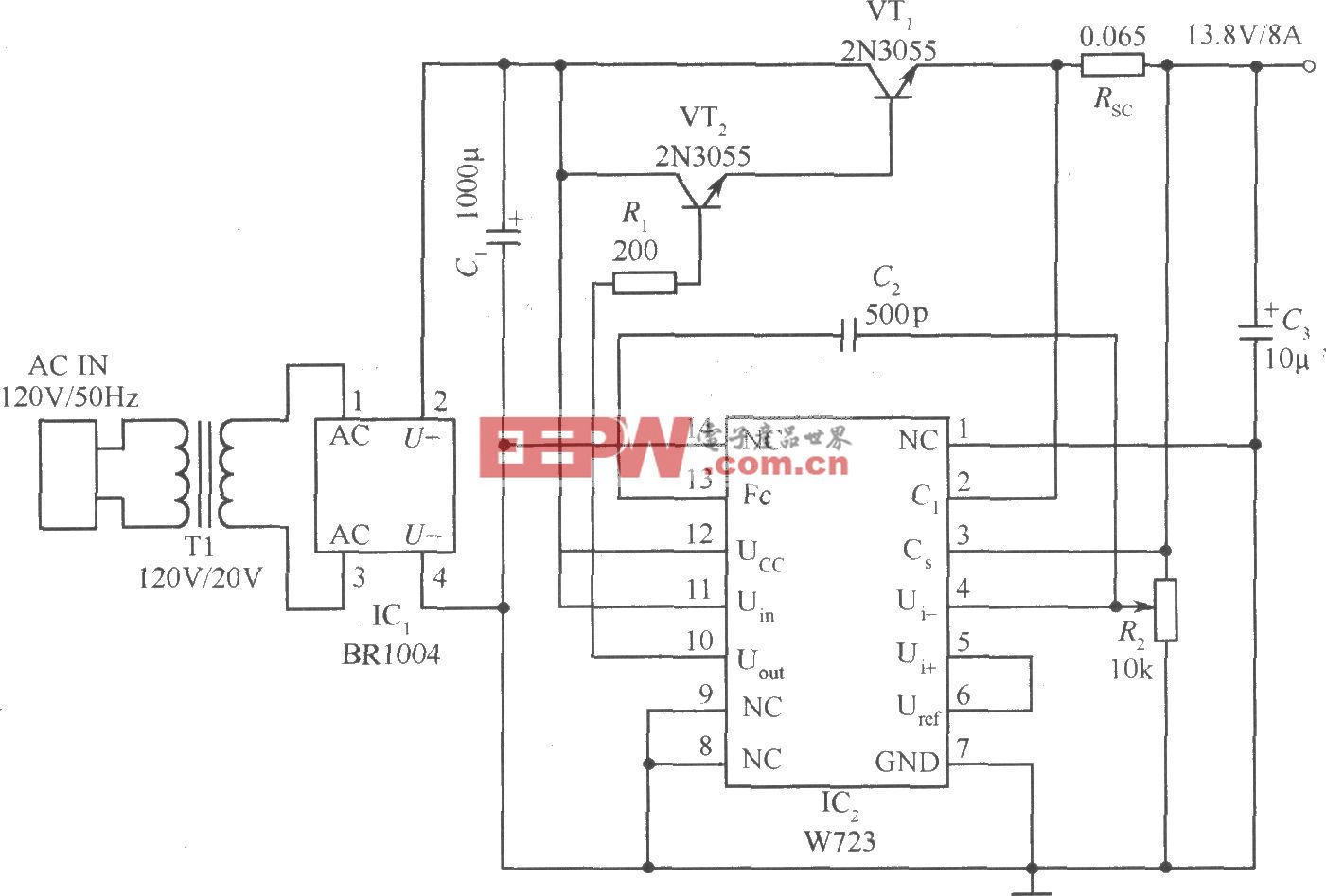

CD4046典型应用电路。

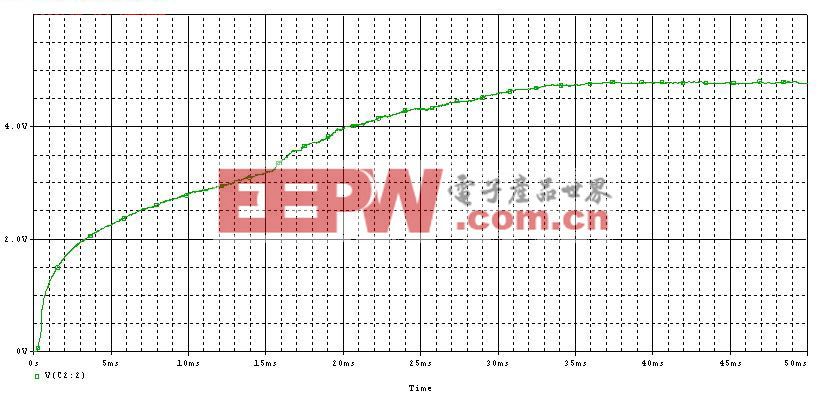

图6是用CD4046的VCO组成的方波发生器,当其9脚输入端固定接电源时,电路即起基本方波振荡器的作用。振荡器的充、放电电容C1接在6脚与7脚之间,调节电阻R1阻值即可调整振荡器振荡频率,振荡方波信号从4脚输出。按图示数值,振荡频率变化范围在20Hz至2kHz。

CD4046的VCO方波发生器

图 6

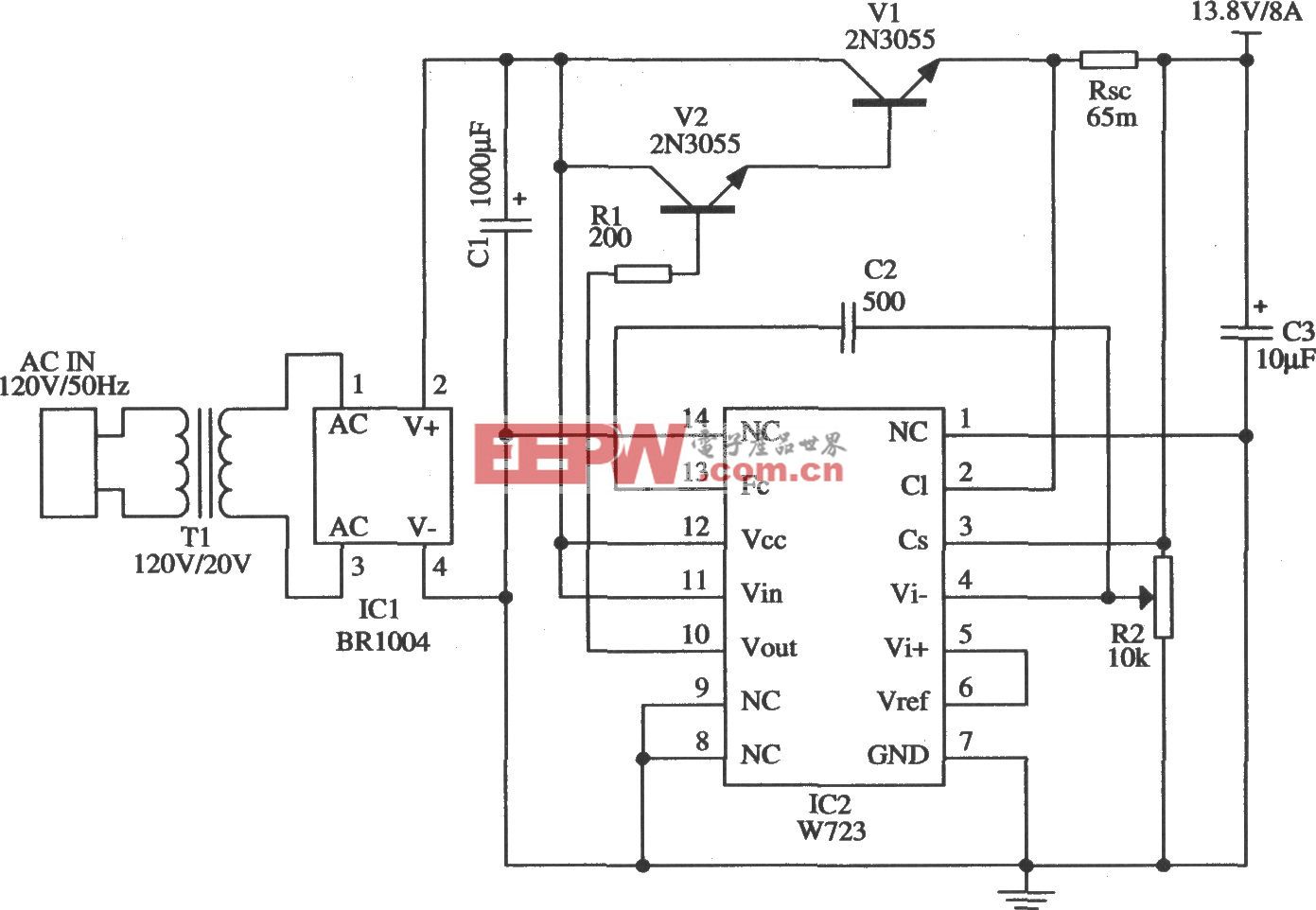

图7是CD4046锁相环用于调频信号的解调电路。如果由载频为10kHz组成的调频信号,用400Hz音频信号调制,假如调频信号的总振幅小于400mV时,用CD4046时则应经放大器放大后用交流耦合到锁相环的14脚输入端环路的相位比较器采用比较器Ⅰ,因为需要锁相环系统中的中心频率f0等于调频信号的载频,这样会引起压控振荡器输出与输入信号输入间产生不同的相位差,从而在压控振荡器输入端产生与输入信号频率变化相应的电压变化,这个电压变化经源跟随器隔离后在压控振荡器的解调输出端10脚输出解调信号。当VDD为10V,R1为10kΩ,C1为100pF时,锁相环路的捕捉范围为±0.4kHz。解调器输出幅度取决于源跟随器外接电阻R3值的大小。

CD4046锁相环调频信号的解调电路

图 7

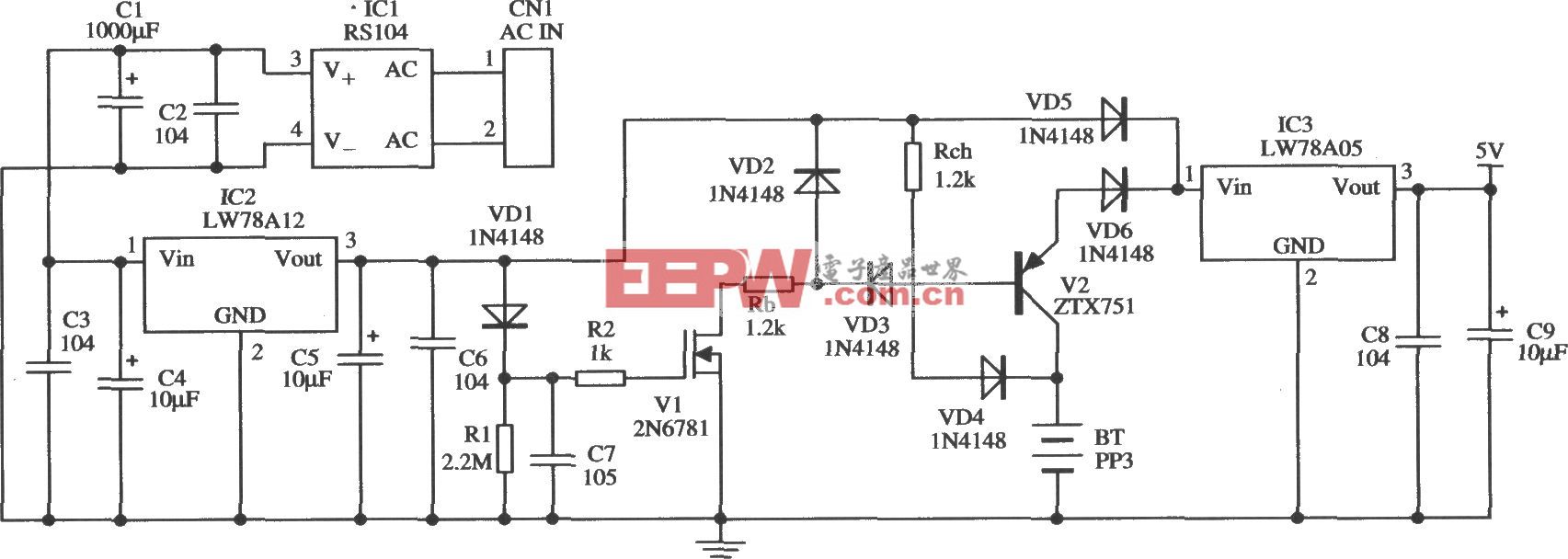

图8用CD4046与BCD加法计数器CD4518构成的100倍频电路。刚开机时,f2可能不等于f1,假定f2f1,此时相位比较器Ⅱ输UΨ为高电平,经滤波后Ud逐渐升高使VCO输出频率f2迅速上升,f2增大值至 f2=f1,如果此时 Ui滞后 U0,则相位比较器Ⅱ输出UΨ为低电平。UΨ经滤波后得到的Ud信号开始下降,这就迫使VCO对f2进行微调,最后达到f2/N=f1,并且f2与f1的相位差Δφ=0°。,进入锁定状态。如果此后f1又发生变化,锁相环能再次捕获f1,使f2与f1相位锁定。

CD4046与BCD加法计数器CD4518构成的100倍频电路

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码