Σ-Δ调制频率合成器

关键词:Σ-△调制,小数分频合成器,锁相环,相位噪声

1 引 言

在通讯技术飞速发展的今天,对信号发生器的要求越益苛刻。同时,随着雷达技术、保密通讯、目标定位、卫星测控、精密制导及电子对抗等现代高技术在军事领域及民用设备中的广泛应用和普及,信号发生器必须要有极高的频率稳定度和频谱纯度。

频率合成技术是现代通讯系统的重要组成部分,它是将一个高稳定度和高准确度的基准频率经过四则运算,产生同样稳定度和准确度的任意频率。频率合成的方法可分为两大类:直接合成法和间接合成法,其形式有:直接频率合成器、锁相频率合成器和直接数字频率合成器。目前应用较普遍的是直接数字频率合成(DDS),其优点是分辨率高、成本低、控制灵活;其主要缺点是输出频率上限不能太高,另外,若设计不合理,由数字技术带来的相位量化噪声和D/A变换器带来的幅度量化噪声所形成的总输出噪声电平可能很高。随着大规模集成电路的发展,利用小数分频频率合成技术解决了单环数字频率合成器中高鉴相频率和小频率间隔之间的矛盾,但小数分频存在严重的小数杂散,通常采用模拟相位内插的方法来抑制。一个理想的系统不要求任何模拟方法来抵消相位噪声和寄生信号,因为这种抵消程度有一定的限度,优于1%的抵消是很困难的。一种完全的数字方案就是引入Σ-△调制技术,该技术是过取样噪声整型和数字滤波技术的结合,

小的频率分辨率的实现依赖于电路的速度,这在当今的技术条件下已成为可能。

Σ-△调制频率合成器是在小数分频锁相环的基础上,采用全数字式Σ-△调制技术来抑制小数杂散,从而克服了模拟相位内插方法的一些缺点如:电路复杂、调试困难、价格昂贵等。它是一种新型的、先进的频率合成器。

2 Σ-△调制技术原理分析

Σ-△调制技术源于广泛应用于音频范围内的高分辨率A/D、D/A转换器中的过取样Σ-△转换技术,其工作原理为:在对信号进行过取样后,噪声功率谱幅度降低,并通过一个对输入呈低通对量化噪声呈高通的噪声整型器,将量化噪声功率的绝大部分移到信号频带之外,而采用过取样移出的噪声不会与信号频谱混叠,从而可通过简单的滤波有效地抑制噪声,比较容易用硬件电路实现。

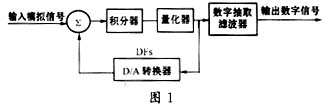

Σ-△A/D转换器是基于将限带输入信号以较高的取样频率进行高速取样,而对每个取样信号量化比特数较低,经常使用一比特量化,这样使Σ-△A/D转换器获得了许多优点,其原理框图如图1所示。其中,减法器、积分器、量化器和D/A转换器组成反馈系统,使得积分器的电压趋于零并使D/A转换器的输出逼近输入值,所得数字输出也逼近输入信号而完成D/A转换,图中取样频率为DFs,Fs为 奈奎斯特取样频率,D远大于一。由于采用过取样,一方面改善了A/D转换器的信噪比,另一方面对抗混叠滤波器的要求也降低。

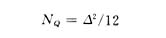

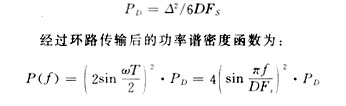

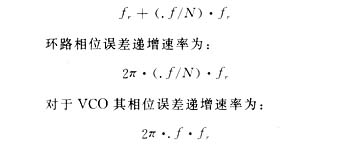

Σ-△A/D转换器是通过提高取样频率和噪声整型来改善信噪比的。当输入信号是随机信号且输入信号幅度大于分层电平(△)时,量化噪声的功率谱密度在0~Fs/2频带内均匀分布,总噪声能量为:

总噪声能量只与量化级幅度有关,与其它因素无关,

而量化噪声功率谱密度与取样频率Fs有关,即:

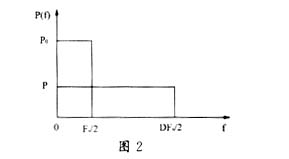

图2为功率谱与取样频率的关系图。显然,如果量化级幅度相同,取样频率越高则功率谱密度越低,即在有用信号带宽内的噪声能量下降为原来的1/D,而有用信号功率是不变的,所以提高取样频率可以提高信噪比。

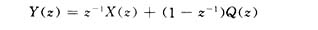

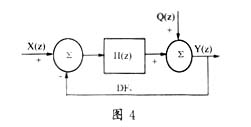

是环路内A/D转换器所产生的量化噪声,并设H(z)为一个单位增益离散时间积分器。对环路进行分析,可得:

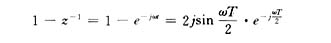

由此可知,环路对输入信号仅产生一个延迟,而对量化噪声进行一个微分处理。将z=ejωT代入量化噪声

的传输因子得:

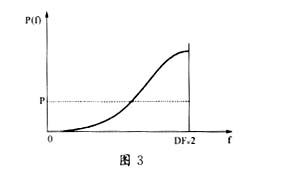

而量化噪声在0~DFS/2之间是均匀分布的,其功率谱密度为:

由此可知,经噪声整型后,量化噪声能量大部分被移向频率高端,而需要提取的有效频率段内的噪声能量大大降低,使输出信噪比得以提高。不难想象,如对量化噪声实现多次微分即可获得更好的噪声整型效果。

在小数分频频率合成器中,所需的小数分频比类似于D/A变换器的模拟输出,而用于控制分频器的数值类似于D/A变换器的数字输入,因此,同样可以将噪声整型原理应用于合成器的小数分频部分,从而可获得更好的带内噪声特性。

3.1 小数分频频率合成器原理分析

在一般的锁相频率合成器中,程序分频器的分频比为整数N,合成器输出频率最小间隔为鉴相频率fr。而对合成器而言,频率间隔应越小越好,由于合成器中鉴相频率不可能无限制地低下去,且为实现快速锁相,要求鉴相频率越高越好。这样就面临着一对不可调和的矛盾。解决这一矛盾的方法是利用小数分频频率合成技术,这一方法已在当今频率合成领域广泛应用。

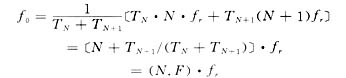

小数分频频率合成器是把VCO输出频率锁定在参考鉴相频率fr的N.F次谐波上。在小数分频器中,整数分频比周期性地从N到N+1地变化,使平均分频比值落在N~N+1区间内。设一个平均周期内,除N的时间为TN,而除N+1的时间为TN+1,则环路锁定后,VCO的平均输出频率f0为:

其中,N为分频比的整数部分,.F为小数部分。

实际使用中可用一累加器的溢出来确定瞬间分频比,设累加器最大容量为C-1,其输入X=.f×C即X/C=.f,因此,当分频器作除N操作时,到相位检波器的VCO信号频率为:

由于累加器求和相同的小数部分,其溢出对应于VCO相位误差超过2π,因此,必须在一个参考循环内改变分频比为N+1以消除VCO的相位差。周期性改变分频比使VCO相位误差呈锯齿波变化,从而形成严重的小数杂散,必须加以滤除。而这种相位误差是可以预测的,可以通过模拟相位内插的方法加以消除。但这种消除是有局限的,且电路相当复杂成本较高。如用Σ-△调制技术对小数杂散进行处理能得到比较理想的效果。

3.2 Σ┐△调制小数分频频率合成器的设计

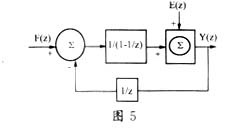

Σ-△调制小数分频频率合成器是对传统的小数分频频率合成器中的小数分频器加以改进,通过多级Σ-△调制器对累加器量化误差进行再次处理从而获得更好的相位误差特性。图5为累加器的数学

模型,显然,相位累加器与一阶Σ-△调制器具有相同的数学模型。虽然累加器作为数字一阶Σ-△调制器对其自身量化误差有一定的滤波作用,但其效果有限,因而传统的小数分频锁相环难以获得较低的

相位杂散。

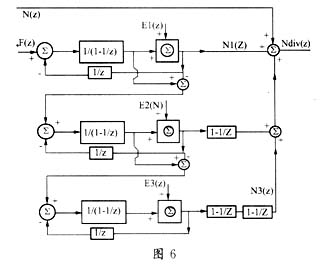

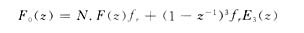

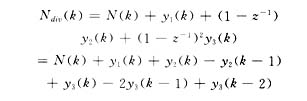

为对小数分频器中引入的量化误差进行有效的抑制,采用级连的高阶Σ-△调制方案,由于每一级Σ-△调制均会引入量化噪声,为实现噪声整型同时考虑到电路稳定性的需要,对引入到下级的量化噪声取反,并逐级增加延迟单元,使下一级Σ-△调制器输出与上一级量化噪声分量相抵消的信号,从而使高阶Σ-△调制器输出中只含N.F和最后一级Σ-△调制器所引入的量化噪声。为简化分析,现以三阶Σ-△调制器为例对相位误差函数进行分析。图6为三阶Σ-△调制Z域模型。原小数分频器中的相位累加器作为第一级调制器。图中N(z)为分频比的整数部分,.F(z)为小数部分,Ei(z)(i=1,2,3)是每级Σ-△调制器引入的量化误差,Ndiv(z)为Σ-△调制器的分频比。由此可得:

N1(z)=

上式说明三阶Σ-△调制器无失真地传输了输入信号N.F(z),并只对第三阶量化误差进行三次微分。所以,这种锁相环的实际输出频率为:

由此式可知,通过三阶整型输出频率抖动的功率谱密度为:

由于锁相环具有较好的低通特性,从而可以消除小数分频杂散。

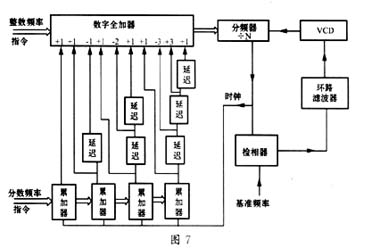

图7为新的频率合成器的原理框图。图中每个累加器的输出和下一个累加器的输入相接,累加器的溢出可以控制分频比。为了减小剩余相位抖动,需合理控制分频比,具体方法是第二个累加器的溢出必

须通过第一个微分控制分频比,第三个累加器溢出通过第二个累加器影响的微分来控制分频比等等。图中输入到程序分频器的瞬间输出为:

这样,在数字电路中可用一组延迟单元和全加器来实现此等式。

整个环路工作原理简单描述如下:压控振荡器频率预置在一个粗值上,经分频器分频(由于要改变分频比来减小剩余相位抖动,此分频器应为双模或四模控制),分频后的频率与基准频率在检相器中比相,产生的差值信号经环路滤波器的积分和滤波,形成一直流控制信号加到VCO上微调VCO输出频率,使其频率准确锁定在预置频率上,其频率稳定度和准确度与基准频率相当。

4 结束语

本设计采用全数字电路来实现Σ-△调制小数分频器,不仅简化了整个系统,而且使频率合成器的性能得到了提高。利用此方法很好地解决了频率分辨率与相位检波器工作频率之间的矛盾,使环路工作频率有了很好的改善,同时大大提高了噪声性能。与传统的小数分频合成器比较,在体积、成本和复杂程度等各方面都有明显的优点。

参考文献

2 J.C.Candy and O.J.Benjamin.The Structure ofQu-antization Noise from Sigma-Delta Modulation.IEEETrans.Commun.,vol.COM-29,pp.1316-1323,Sept.1981

关键词: 调制

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码