煤岩声发射监测,又名微震监测,是一种公认的很有发展前途的连续预测煤矿动力灾害的方法。目前国内已经有多套国产和引进的系统投入使用。其中,煤岩声发射信号的采集是该监测系统实现的重要环节之一,它要求数据采集电路具有大动态范围、多通道同步数据采集等特点。目前,国内已有多家单位进行了相关的研究工作:熊庆国等采用单片机+DSP的方案研制出便于携带的具有16位分辨率的单通道岩体声发射监测仪;周凤星等采用C8051F022核心控制器,设计出能够同步采集三路16位分辨率加速度传感器信号的声发射数据采集站:潘一山等研制的矿震监测定位系统采用了16位、8通道的数据采集器;王继强等以TMS320VC5402处理器,分别设计了8通道、16位分辨率的微震实时监测系统。

随着技术的快速发展,处理器和A/D转换器的性能都在不断改善,使得更多通道、更高分辨率的煤岩声发射信号采集成为可能。TMS320 VC5509A是TI公司推出的一款低功耗、高性能、16位定点DSP处理器,其主频最高可达200 MHz,具有丰富的外设,适用于大量数据的数据采集和处理。ADS1278是TI公司推出的一款工业级的24位分辨率、8通道同步A/D转换器,具有优良的AC和DC性能,采样率最高可以达144 ksps,并且可通过菊花链的方式级联多片,实现更多通道的数据采集。文中以DSP处理器TMS320VC5509A为核心,通过菊花链的方式扩展了2片ADS12 78,实现了24位分辨率、16通道同步数据采集。

1 数据采集电路的工作原理

数据采集电路的结构框图如图1所示,其工作原理为:系统上电后,TMS320VC5509A(以下简称VC5509A)首先完成对自身资源的配置,然后通过I2C总线配置PCA9535的I/O口状态,完成对ADS1278的基本配置。待以上准备工作完毕后,VC5509A发出一个同步转换脉冲,启动A/D转换;这时,前端传感器采集的煤岩声发射信号经过信号调理电路放大、滤波等预处理后送入ADS1278进行数据转换。最后,各通道转换后的数据以时分复用的形式送入VC5509A的McBSP端口,完成数据的采集。

由数据采集电路的原理框图可以看出,VC5509A与ADS1278的接口是该设计的核心。该接口电路按功能划分为两部分:一个是控制接口,用于设置ADS1278的工作模式、数据传输模式和通道使能情况:另一个是数据接口,用于传输ADS1278采集的数据。此外,电源和基准电路也是该数据采集电路的重要组成部分,下文将详细介绍。

2 数据采集电路的硬件实现

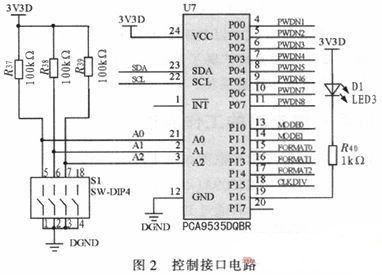

2.1 VC5509A与ADS1278控制接口电路设计

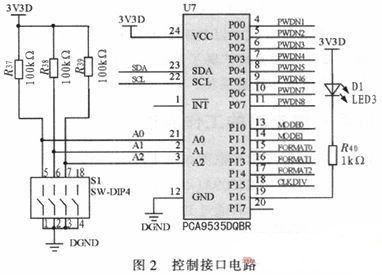

ADS1278的工作模式、数据输出模式和通道使能都是通过引脚来设定的,每片需要设置的引脚多达14个。倘若采用VC5509A的I/O口完成配置,势必造成很大的资源浪费。本文通过VC5509A的I2C控制器挂载了两片PCA9535来完成对ADS1278的配置,只占用两个引脚。

图2给出了单片ADS1278与VC5509A的控制接口电路,其中,3位拨码开关用于设置PCA9535的I2C地址;PWDN[8:1]用于设置各通道的开启情况;MODE[1:0]用于设置工作模式;FORMAT[2:0]用于设置串行数据输出的传输协议和数据格式;CLKDIV用于设置时钟是否减半;LED指示引脚连接一个用户指示灯,当向对应的I/O口写入低电平时,该指示灯点亮,可据此观察PCA9535配置是否成功。

2.2 VC5509A与ADS1278数据接口电路设计

ADS1278转换后的数据以串行方式通过引脚输出,可以通过FORMAT[2:0]来选择传输协议和数据格式。本文通过VC5509A的McBSP外设接口来接收ADS1278转换后的数据,该接口同时支持SPI和帧同步协议,能够方便的实现ADS1278的无缝连接。相比较而言,帧同步模式拥有更快的传输速度,所以本文选择了帧同步协议。

VC5509A与ADS1278采用帧同步协议的数据接口电路如图3所示,两片ADS1278以菊花链的方式级联。其中,U3的输入DIN接地,DOUT1连到U2的DIN输入;U2的输出DOUT1经D触发器后连到VC5509A的DR1引脚;U2和U3拥有相同的CLK、SCLK、SYNCn和FSYNC控制信号。

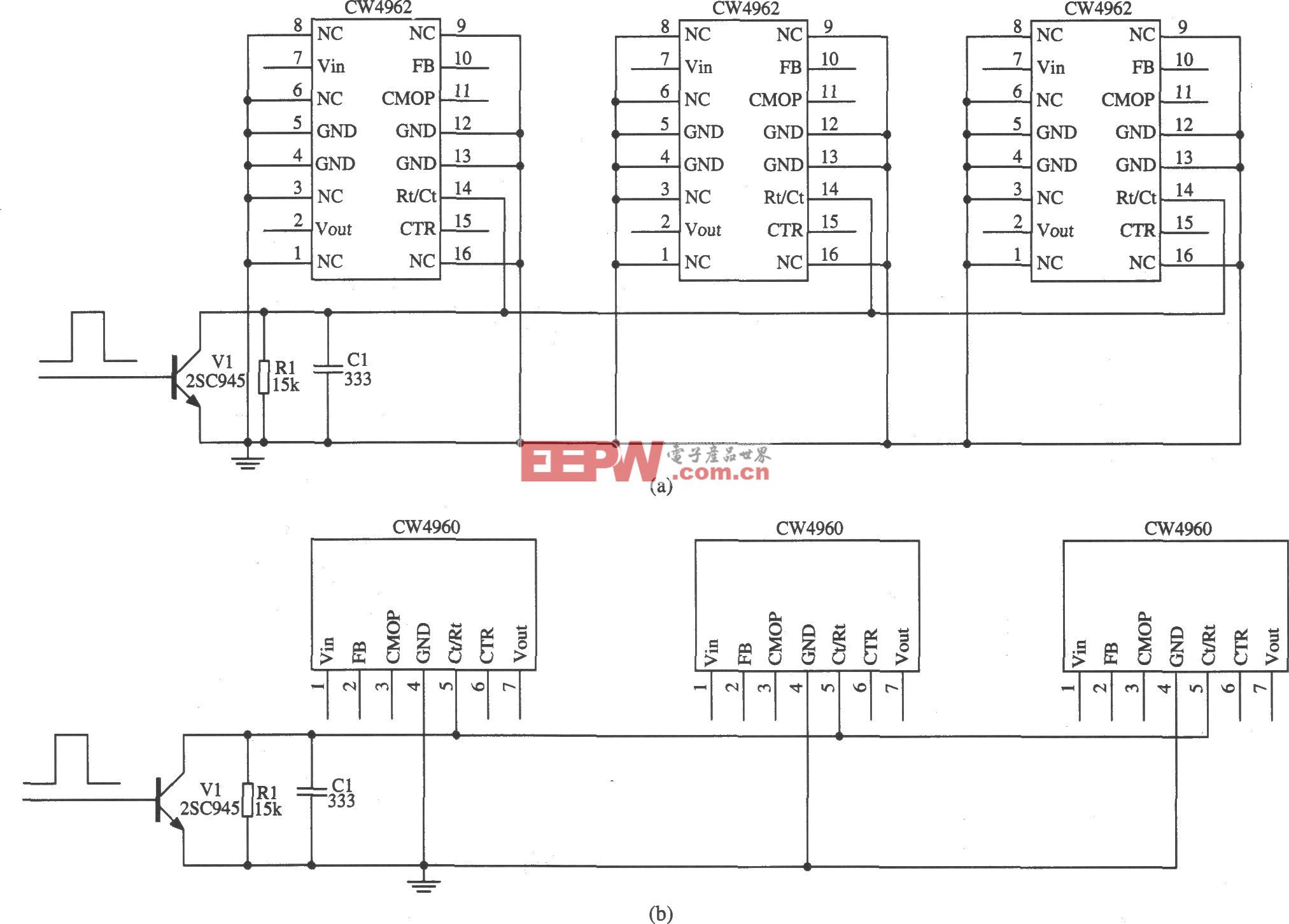

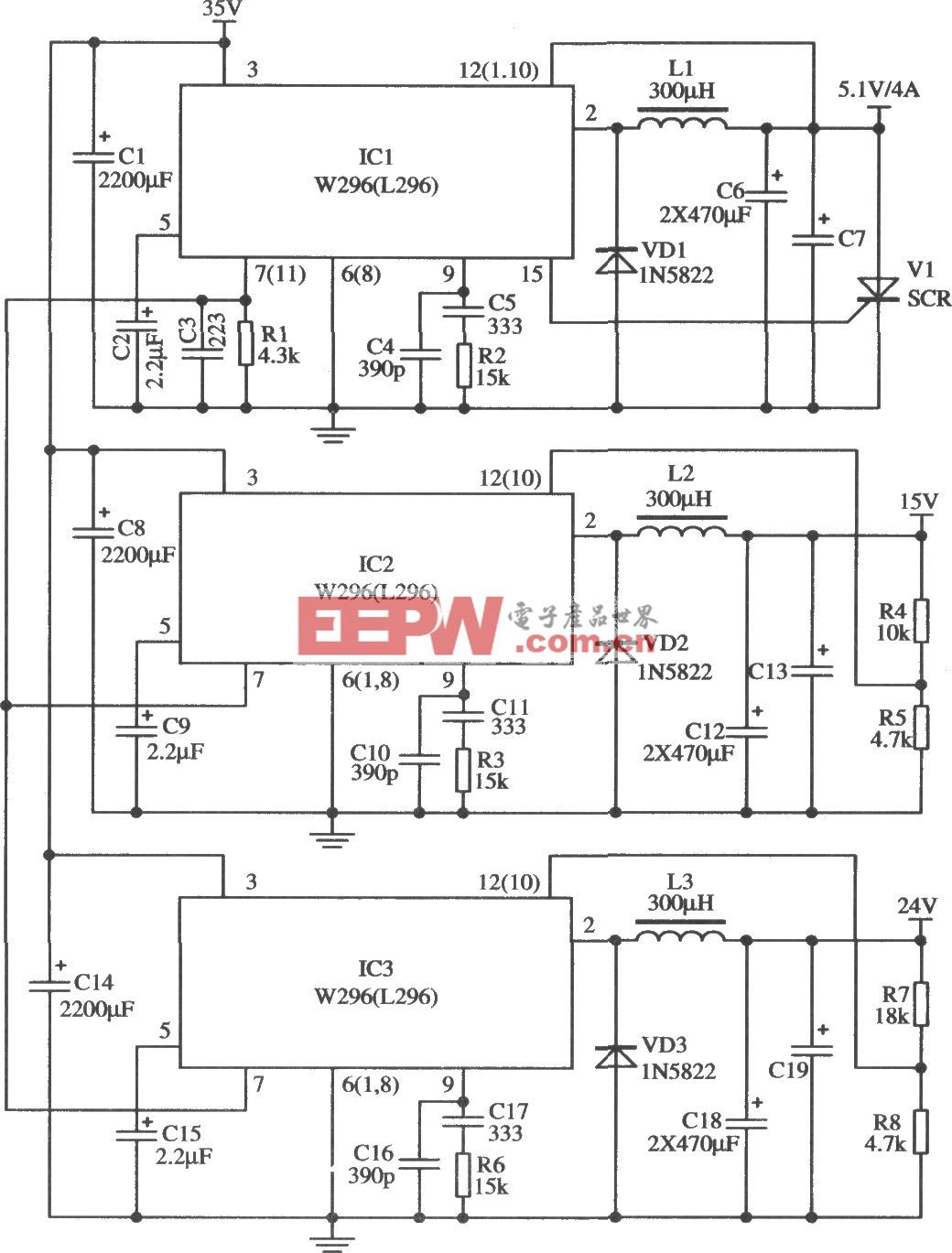

2.3 电源和基准电路设计

稳定、低噪声的电源是实现高精度数据采集的必要保证,该数据采集电路包含3种典型电源:ADS1278的1.8 V内核电源,3.3 V I/O口电源和5 V模拟电源。其中,5 V模拟电源通过具有较小纹波的LM7805线性稳压得到:3.3 V和1.8 V数字电源通过具有高电源抑制比和低噪声性能的电源芯片TPS73033和TPS73018获得。

基准电路在高精度数据采集电路的设计中起着至关重要的作用,它会直接影响到数据采集电路的精度和稳定性。本文采用了TI公司的一款低噪声、低温漂、精度极高的电压基准芯片REF5025为ADS1278提供参考电压。为使REF5025的输出性能达到最佳,在将基准信号送入ADS12 78之前添加了一级调理电路,用于进行阻抗匹配和滤波。

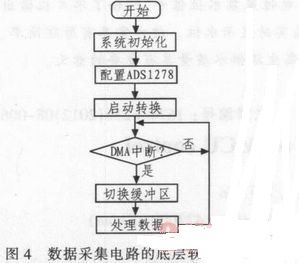

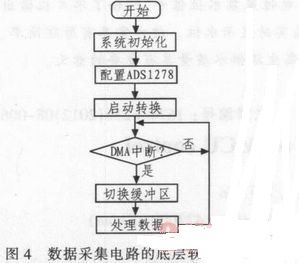

3 数据采集电路的底层软件实现

数据采集电路的底层软件实现包括配置和数据采集两部分。其中,配置又可分为两部分:一是对VC5509A本身的初始化,包括:CSL库、PLL、GPIO、I2C、定时器、McBSP、DMA和中断等:二是对ADS1278参数的设置,包括通道开启情况、工作模式和采样率等。数据采集工作主要是由DMA来完成的,CPU只负责切换缓冲区和处理数据等操作。

数据采集电路的底层软件工作流程如图4所示。系统上电后,首先完成初始化和ADS1278的配置工作;然后,CPU发出同步转换脉冲,启动数据转换,进入中断等待状态;与此同时由DMA来进行数据采集,当DMA存满缓冲区后触发中断;CPU进行切换缓冲区和数据处理等操作,然后返回等待下一次中断。

在上述过程中,DMA和CPU是并行工作的:即DMA专门负责存储数据,将数据搬移到缓冲区:而CPU则负责切换缓冲区并处理缓冲区内的数据。但同一时刻,CPU和DMA操作的是不同的缓冲区:当DMA向缓冲区0存储数据时,CPU处理缓冲区1的数据:而DMA向缓冲区1存储数据时,CPU处理缓冲区0的数据。这样DMA和CPU实现了一种“乒乓”切换操作,使得DSP能够更加专注于数据处理,从而能够发挥最佳性能。

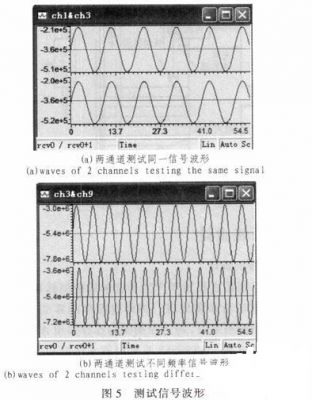

4 数据采集测试结果

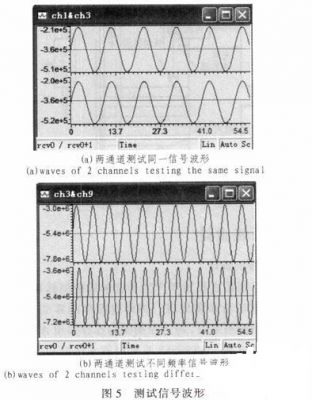

由于数据采集电路的通道数众多,无法一一展示测试结果,所以本文选取了两组典型通道,分别测试同一信号和不同频率的信号。用CCS集成开发环境进行硬件仿真,在DMA中断里设置断点,并通过Graph工具调取缓冲区内的数据显示采集信号波形,结果分别见图5(a)、(b)所示。测试中,设置ADS1278的采样频率为9 375 Hz,显示缓冲区大小为1 024个点,图中的横坐标是经换算过后的时间信息,单位是ms,纵坐标是A/D转换后的实际数值。

图5(a)中的测试信号频率为100 Hz,幅值为100 mVpp。由图可以看出,两通道采集的信号波形一致,相位相同,说明了两通道采样的同步性。图5(b)中,通道3信号频率为200 Hz,幅值约为1.45 Vpp;通道9信号频率为300 Hz,幅值为1.1Vpp。根据图中数据可以计算出,通道9的信号频率约为通道3的1.5倍,信号幅值约为通道3的1.3倍,与测试信号对应,这说明了两通道采集不同信号的正确性。图5(a)和(b)两图中的信号连续光滑,没有突变点,这也说明了采集电路的高性能。

5 结论

文中面向煤岩声发射信号采集,提出了一种大动态范围、多通道同步数据采集电路的解决方案。该方案通过较少的接口既实现了多通道数据的同步采集,又可灵活开启各通道、设置工作模式和采样率等。采用本数据采集电路的方案,还可方便增加ADS1278到8片,将通道数扩展到64个,进而实现更多通道数据的同步采集。但在使用时需注意,该数据采集电路可扩展的通道数会受到工作模式和工作时钟频率的制约。

关键词:

声发射

高精度

DSP

多通道

同步

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码