碳化硅MOSFET的短路实验性能与有限元分析法热模型的开发

摘要:本文的目的是分析碳化硅MOSFET的短路实验(SCT)表现。具体而言,该实验的重点是在不同条件下进行专门的实验室测量,并借助一个稳健的有限元法物理模型来证实和比较测量值,对短路行为的动态变化进行深度评估。

前言

就目前而言,碳化硅(SiC)材料具有极佳的的电学和热学性质,使得碳化硅功率器件在性能方面已经超越硅产品。在需要高开关频率和低电能损耗的应用中,碳化硅MOSFET正在取代标准硅器件。半导体技术要想发展必须解决可靠性问题,因为有些应用领域对可靠性要求十分严格,例如:汽车、飞机、制造业和再生能源。典型的功率转换器及相关功率电子元件必须严格遵守电气安全规则,要能在恶劣条件下保持正常工作,其鲁棒性能够耐受短路这种最危险的临界事件的冲击 [1]。

没有设备能够监测微秒级功率脉冲引起的器件内部温度升高,当脉冲非常短时,只能用模拟方法估算晶体管结构内部和相邻层的温度上升。此外,温度估算及其与已知临界值的相关性将能解释实验观察到的失效模式。

在这种情况下,模拟工具和分析方法起着重要作用,因为了解在极端测试条件下结构内部发生的现象,有助于解决如何强化技术本身的鲁棒性问题,从而节省开发时间[2],[3]。

本文简要介绍了650V、45mΩ碳化硅功率MOSFET样品的短路实验,以及相关的失效分析和建模策略。

短路试验分析与结构模拟

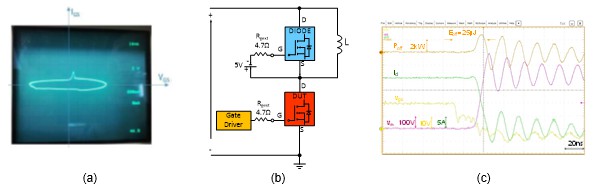

在做短路实验(SCT)前,先用电压电流曲线测量仪对待测样品的栅极氧化层进行完整性测试,如图1(a)所示。然后,对待测器件进行动态表征测试,评估其开关特性。 图1(b)所示是典型开关表征的等效电路图。图1(c)所示是相关实验的波形:Vgs、Vds、Id,以及在VDD = 400V、20A负载电流、Vgs=-5/20V、Rg =4.7Ω关断时的功率分布Poff。计算出关断能量Eoff,取值约25J。

图1(a)栅极氧化层测量,(b)开关表征等效电路(c)典型的关断波形

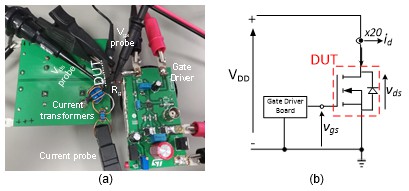

图2(a)所示是短路实验的试验台,图2(b)所示是实验等效电路图。

图2实验装置:(a)试验台,(b)等效电路

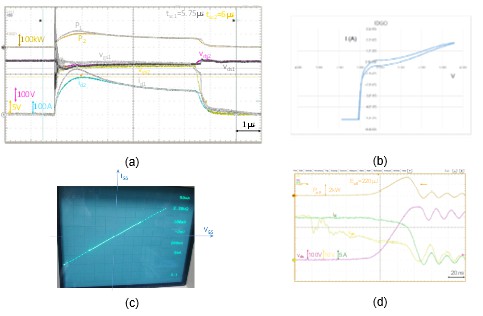

图3(a)所示是样品1在失效条件下的短路实验波形。施加一串时间宽度增量为250ns的单脉冲达到失效点。观察到脉冲间延迟为5秒。在VDD = 400V、Vgs = 0/20V和Rg =4.7Ω的条件下,样品1顺利完成tsc=5,75s脉冲短路实验。

图3(a)短路试验动态波形 (b)和(c)栅极氧化层电学表征(d)短路试验导致栅极氧化层退化后的关断波形

在这个时步里,脉冲无法显示失效模式,需要在下一个时步(tsc=6s)中去验证,此时,栅极氧化层被不可逆地损坏。观察到漏极电流Id和Vgs下降(图3(a))。在图3(b)中观察到的损坏是短路能量(Esc)过高导致的栅极氧化层失效,并且用曲线测量仪证实失效存在,如图3(c)所示。观察到的栅极氧化层退化与Eoff性能的动态变化相关,如图3(d)所示。

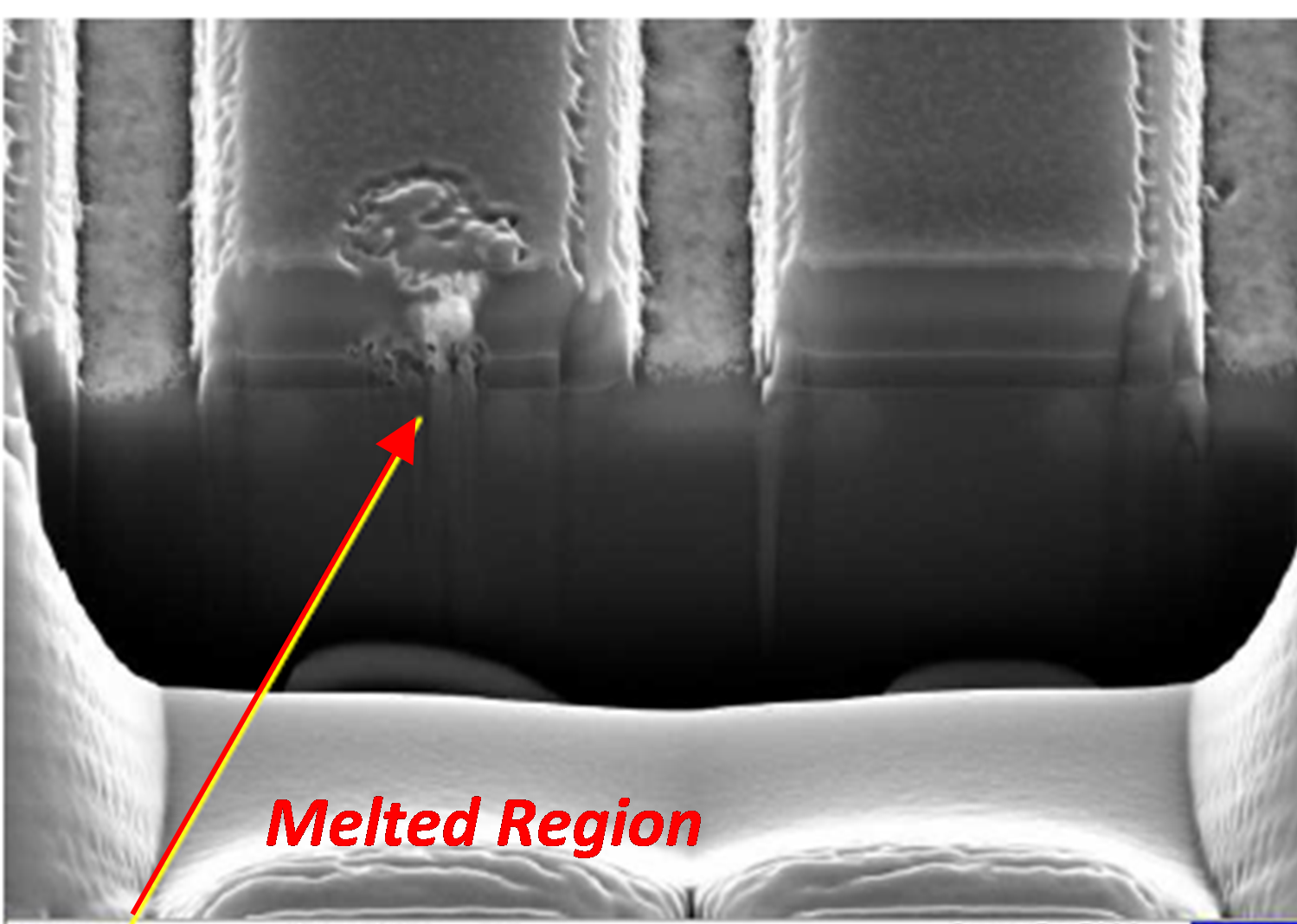

随后,对失效器件进行失效分析,在后侧和前侧用光电子能谱确定缺陷位置,并用聚焦离子束方法进行“热点”截面分析。 图4所示的物理缺陷本质上是多晶硅层熔化,与电废料一致。

图4:退化后物理分析

关键词: 碳化硅(SiC)MOSFET 短路 热模型

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码