Mentor Catapult HLS 助力Chips&Media 将深度学习硬件加速器 IP 交付时间缩短一半

Mentor®, a Siemens business 今日宣布 Chips&Media™ 已成功部署 Mentor Catapult™ HLS 平台,将使用深度神经网络 (DNN) 算法设计和验证其 c.WAVE 计算机视觉 IP 的实时对象检测。Chips&Media 是一家面向片上系统 (SoC) 设计高性能、高质量视频 IP 的领先供应商,其产品广泛应用于汽车、监控和消费电子领域。

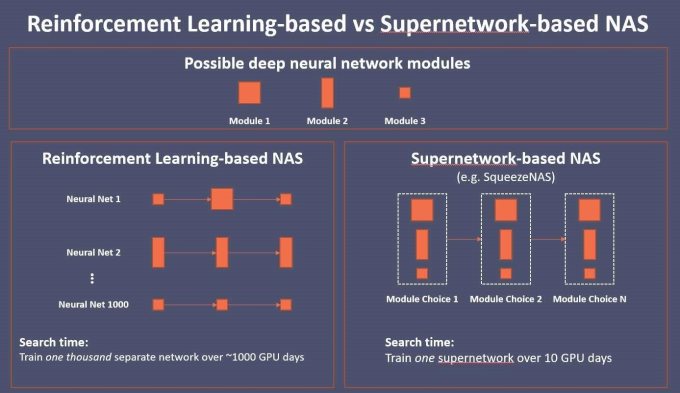

Chips&Media 需要通过减少功能验证时间、时序收敛、自定义和最终优化来大幅提高生产力,把更多时间用于机器算法和架构的研发上,从而为客户快速提供差异化的机器学习 IP。为实现这些目标,他们弃用了传统的手工编码寄存器传输级 (RTL) 流程,转而采用 Catapult HLS 平台,以使用 C 语言编写算法和验证平台。与同一项目中使用 RTL 流程的团队相比,HLS 设计和验证团队将项目时间缩短了一半。

“要应对以推理为目标的设备带来的加速挑战,我们认为关键在于使用深度神经网络建立一个专注于功耗、性能和面积 (PPA) 并高度优化的硬件架构,”Chips&Media 首席技术官 Mickey Jeon 表示。“HLS 使我们能够极其高效地完成这项工作。我们的项目取得了突出的成绩,我们计划在接下来的项目中部署应用 Catapult 的 HLS 流程。”

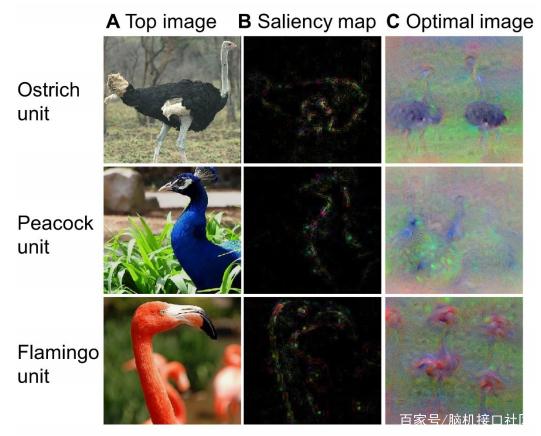

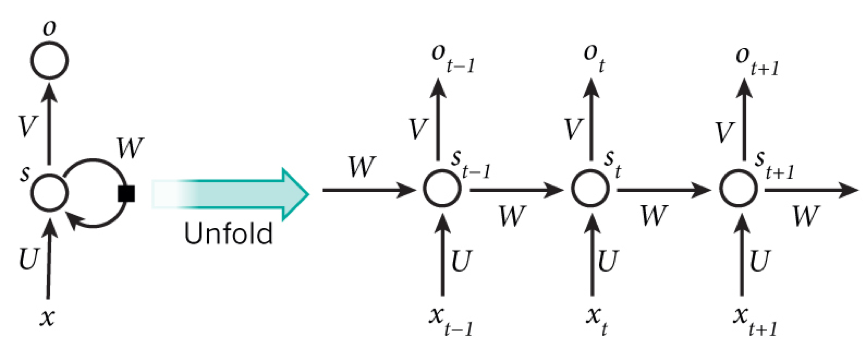

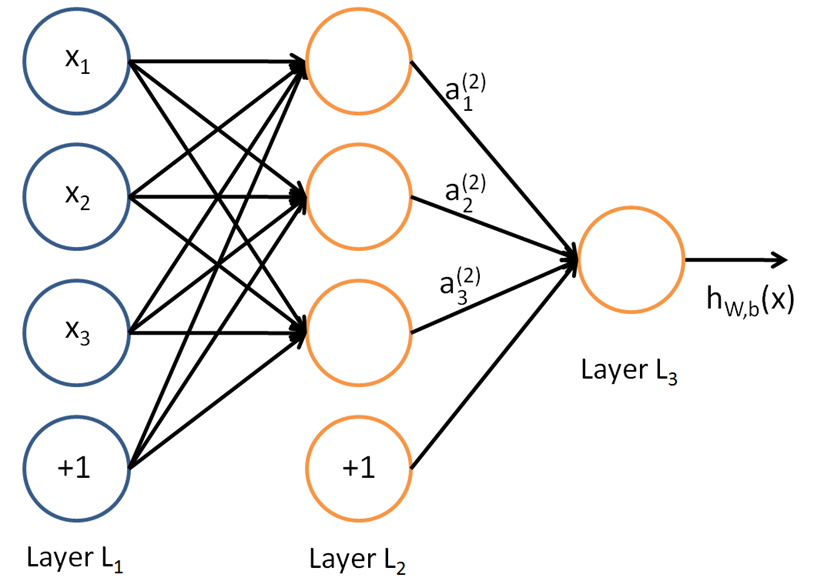

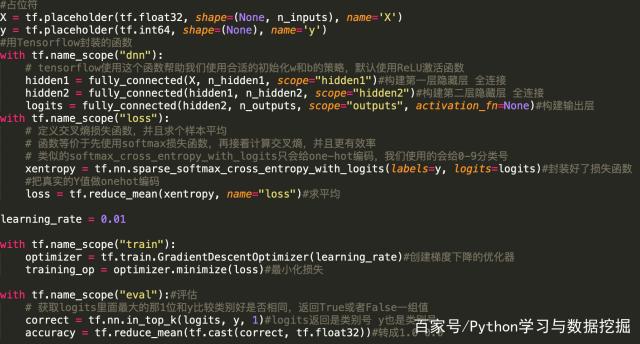

基于 DNN 的计算机视觉处理的特征,就是乘法/加法/累加的重复计算,同时通过神经网络层进行大量数据迁移。DNN 是在 Caffe 或 TensorFlow™ 等框架上开发的,然后在 C 模型中捕获其算法。Chips&Media 将此算法 C 模型改进为可综合的 C 代码,并使用 Catapult HLS 平台快速探索各种架构并综合到 RTL 中,以找到此类设计的最佳解决方案。

“根据我们的观察,在市场快速变化的多个应用领域,采用 Catapult HLS 是提高生产力来获得成功的唯一途径,”Mentor 数字设计和实施解决方案总经理 Badru Agarwala 表示。“我们一直与 Chips&Media 密切合作,以确保他们平稳过渡到 HLS。该平台可以让他们专注于算法/架构设计,而不是底层实现和调试等细节,从而更快地把想法变成产品,然后推向市场。”

有关更多详细信息,请参阅详细的案例研究:《Chips&Media:深度学习对象检测 IP 的设计和验证》。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码