信号完整性分析基础系列之三--串行数据测试中的CDR

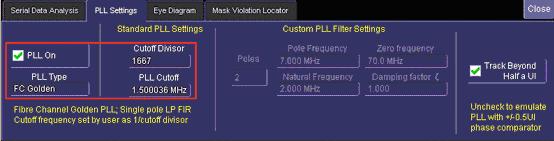

如下图4所示为力科串行数据分析仪中PLL设置的参考,缺省情况下使用FC Golden PLL,该PLL为1阶锁相环,其环路带宽等于比特率除以1667,最早是在Fibre Channel的MJSQ文档中定义的。

图4:力科串行数据分析仪的软件CDR设置界面

如下图5为使用力科示波器测量某2.5Gbps信号,当示波器的串行数据分析软件的PLL带宽在2MHz、5MHz、10MHz、20MHz四种设置下的眼图测量结果,可见,PLL带宽越高,眼图越清晰,抖动越小。问题是,待测试电路的收发器RX端接收到的、真实的眼图和抖动是什么样呢?答案是必须把示波器的CDR参数设置得和待测试电路RX端的CDR参数完全一致,这样示波器的测量结果才具备参考价值。

图5:示波器在不同PLL设置时测量同一信号的眼图

在图4和图5中都是一阶锁相环的CDR,在很多的串行电路标准中都使用这类PLL,比如GBE、XAUI、SDH、CPRI、FC、SAS等等。不过,PCIe Gen2、SATA2、Displayport则使用了二阶锁相环的CDR,如图6所示为一阶PLL和二阶PLL的JTF对比,二阶PLL有更加陡峭的滚降系数-40dB/decade(一阶PLL的滚降系数为20dB/decade)。假设某500kHz的抖动为150ps(而且500kHz在斜线的频段内),通过一阶PLL后抖动只有15ps,而通过二阶PLL后仅为1.5ps。可见,对于图6中低频段的抖动,二阶PLL可以更大幅度的降低该频段的抖动。

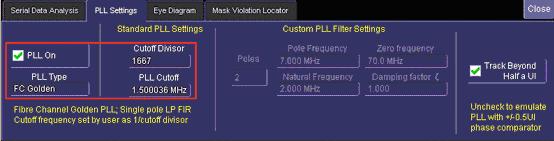

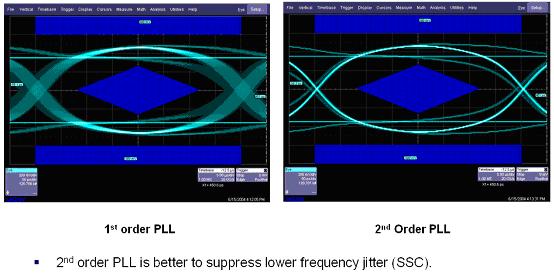

图7所示为某2.5Gbps信号,CDR使用一阶PLL或二阶PLL的眼图测量结果,可见,使用二阶PLL得到的眼图非常清晰、抖动更小。二阶PLL可以更大程度的减小低频抖动,通常用于带有扩频时钟(SSC)的串行数据信号,比如计算机主板上的SATA和PCIe。

图7:示波器在不同PLL设置时测量同一信号的眼图

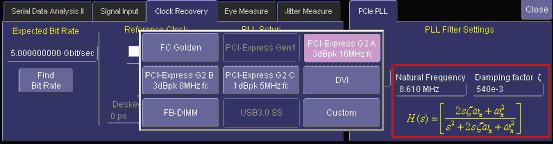

如下图8所示,在力科SDA中,集成了FC Golden, PCIe Gen1, PCIe Gen2, DVI, FBDIMM, USB3.0和Custom多种PLL参数设置,测量时根据待测试信号的类型选择合适的CDR设置。

图8:力科示波器集成了多种PLL设置

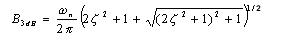

在Custom自定义锁相环模式下,可以选择1阶PLL还是2阶PLL。如果是自定义的1阶PLL需要设置极点和零点的频率,PLL的截至频率就是极点频率,零点频率必须高于前者,其决定了阻带的衰减系数;如果是自定义2阶PLL需要设置Natural Frequency(ωn)和Dampling factor(ζ),如图8红色标记所示,该PLL的环路响应的传递函数为H(s)(图8中黄色字体的公式),截至频率可用下面的公式计算:

综上所述,正确设置示波器的CDR参数是测量眼图和抖动的关键,测试人员需要参考串行数据规范或仪器厂商的操作文档,才能保证测量的准确性和有效性。

参考文献

1, Fibre Channel – Method Jitter and Signal Quality Specification – MJSQ, T11.2/Project 1315-DT/Rev 14.1, June 5, 2005.

2, Mike Peng Li, "Jitter, Noise, and Signal Integrity at High-speed".

1

2

关键词: 信号完整性串行数据CD

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码