SPI总线小结

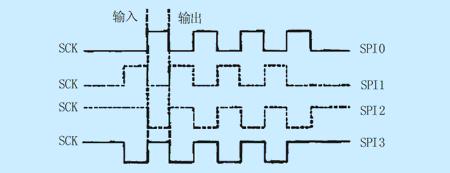

关于时序分析,网上有几张流行的说明图表,意义是相同的。

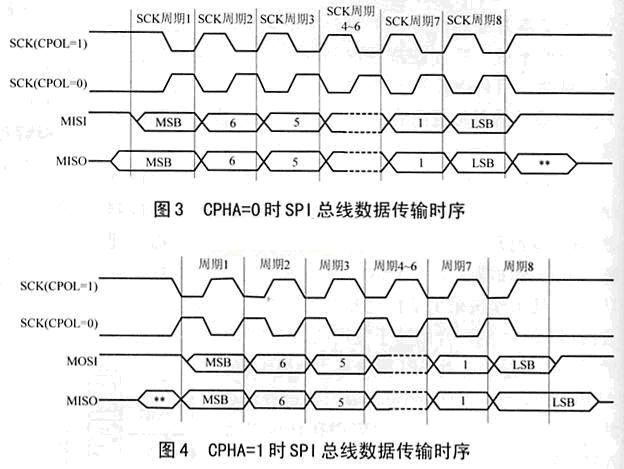

图2 SPI时序分析

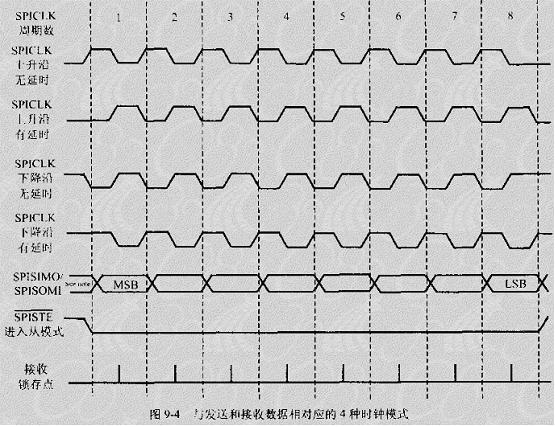

图4 SPI时序分析

虽然表述的侧重点不同,但描述的意思是一致的。根据SCK无效电平和采样时刻的不同,2x2=4种时序。

4、注意事项

1)在Mcbsp的手册中,SPI的时序表述有所不同。SCK无效电平表述是相同的,但是采样时刻的表述她是通过有无delay来表达的。对比如下:

CPHA = 0表示在每个周期的第一个时钟沿采样,对应存在delay;

CPHA = 1表示在每个周期的第二个时钟沿采样,对应无delay。

2)在不同场合下,发送和接收的表述词汇可能不同。比如:

发送可表述为:transmit,output

接收可表述为receive,sample,latch

3)SPI主模块和从设备时钟相位和极性应该一致。个人理解这句话有2层意思:其一,主设备SPI时钟和极性的配置应该由外设来决定,也就是说主设备这边的时钟极性和相位都是以从设备为基准的;其二,两者的配置应该保持一致。

1

2

关键词: SPI总线时序分析串行外围接

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码