高速数据采集系统中精确时标的CPLD实现方法

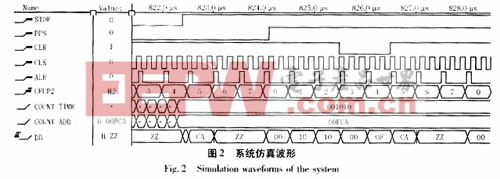

其仿真结果如图2所示。

4 结论

本文对高速数据采集系统中的采集数据贴上精确时间标签的方法进行了详细地叙述和仿真,得出如下结论:

(a) 假设高速AD转换器件的转换频率为5MHz,则本系统能为存入静态RAM中的转换数据贴上精度为0.2μs的时间标签。

(b) 通过复杂可编程逻辑器件(CPLD)间接地实现了“低速”的单片机系统对高速数据采集系统的实时监视。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码