加减法运算电路的设计方法

解出R’=40kΩ。

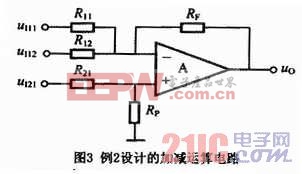

例2,试设计实现u=2u121-3u111-u112运算关系的加减运算电路。

将所要实现的运算关系式与式(4)对比,确定式(4)中各输入信号的比例系数为

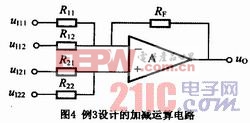

例3,试设计实现u0=2u121+u122-1.5u111-0.5u112运算关系的加减运算电路。

将所要实现的运算关系式与式(4)对比,确定式(4)中各输入信号的比例系数为

确定所设计电路的形式为图1中去掉电阻R’及Rp,按四个输入信号重画如图4所示。

选取RF=150kΩ,代入各输入信号的比例系数表达式中,解出

4 结语

本文讨论了加减运算电路的构成形式及比例系数适应范围,从而可实现输入信号以任意比例系数参与运算的电路设计,使运算电路具有普遍适用性。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码