FPGA电路设计: 如何应对电源相关问题的挑战

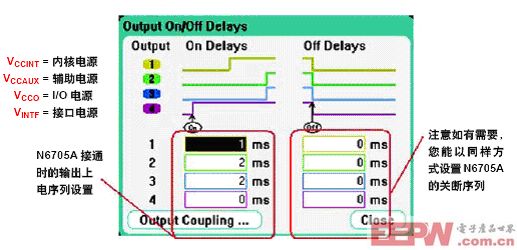

首先按照 图2 所示,为FPGA电路设置上电时序,VINTF 最早打开输出,VCCINT 在VCCO 之前1毫秒打开供电:

图2 N6705A上电序列设置屏

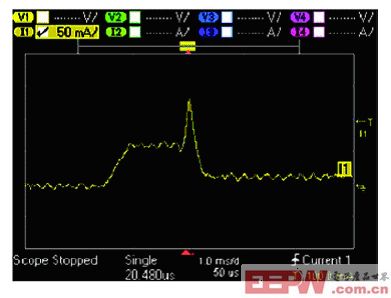

在此供电情况下,可以看到内核电源消耗的电流 ICCINT 在上电过程中产生一个明显的脉冲尖峰,如图3 所示:

图3 内核电源VCCINT在上电过程中所消耗的电流波形ICCINT

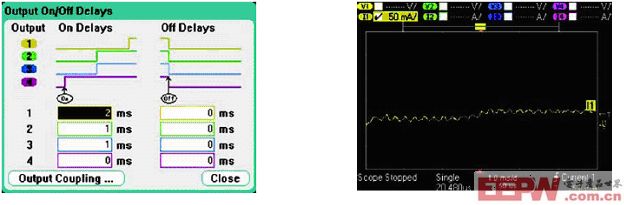

按图4 所示重新改变上电时序,使VCCINT上电输出滞后于VCCAUX 1毫秒,此时可以看到ICCINT 电流波形中脉冲尖峰已经消失。

图4 调整上电时序后,ICCINT 的电流波形

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码