74ls373中文资料

作者:dolphin

时间:2016-09-30

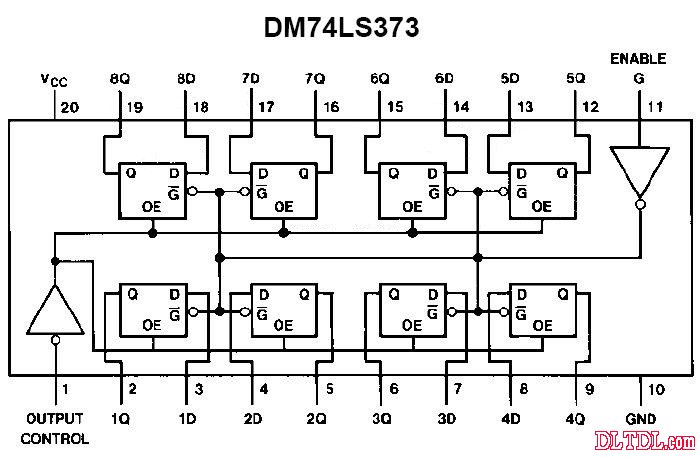

54LS373 /74373 三态缓冲输出的8D锁存器(3S,锁存允许输入有回环特性)

54LS373/74LS373 17ns 120mW

54LS373/74LS373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总

线。当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但

锁存器内部的逻辑操作不受影响。

当锁存允许端 LE 为高电平时,O 随数据 D 而变。当 LE 为低电平时,O 被锁存在

已建立的数据电平。

当 LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善 400mV。

图1引脚功能图

管脚引出端功能符号

D0~D7 数据输入端

OE 三态允许控制端(低电平有效)

LE 锁存允许端

O0~O7 输出端

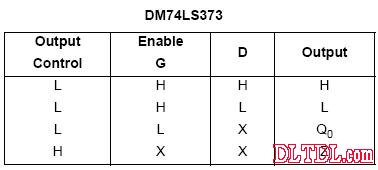

真值表:

L--低电平;

H--高电平;

X--不定态;

Q0--建立稳态前Q的电平;

G--输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE--使能端,接地。

当G=“1”时,74LS373输出端1Q-8Q与输入端1D-8D相同;

当G为下降沿时,将输入数据锁存。

图2 54LS373/74LS373内部逻辑电路图

74ls373引脚图-引脚功能-74ls373作用54ls373参数

关键词: 74ls373中文资料 电路图 电路图技术资料 电路图设计资

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码