一种使用连续时间Σ-Δ型转换器优化信号链的新型方法

问题:

为何应考虑使用CTSD ADC来改善我的信号链设计?

答案:

相比传统架构,CTSD拓扑能够优化信号链。

当今许多应用要求小尺寸,同时保持同样的性能。开发人员经常面临如何实现这一目标的问题并且经常要做出妥协。举例来说,通过牺牲噪声性能或精度来减小尺寸。本文探讨使用连续时间Σ-Δ型(CTSD)转换器优化设计、降低物料(BOM)成本和减小尺寸的新型方法。

要让所需的传感器或信号达到最佳效果,必须保证信号链中的所有元件配合出色。从传感器到模数转换器(ADC)通常使用几个分立元件。除了传感器和ADC,还经常使用仪表放大器、ADC驱动器、基准电压源缓冲器和滤波器。尤其要注意的是,ADC驱动器的选择和滤波器设计通常是造成误差的来源,但这两项通常会被低估。

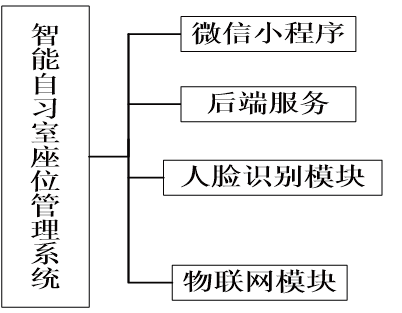

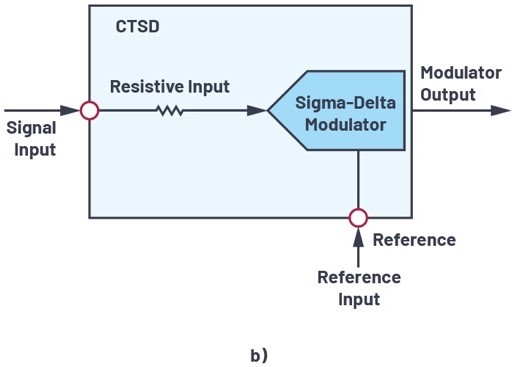

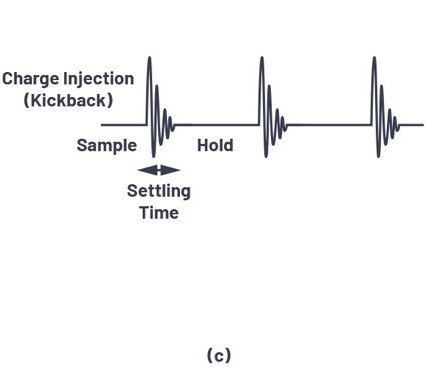

图1 (A)离散时间ADC拓扑,(b)连续时间Σ-Δ型转换器,(c) 通过开关电容输入级的电荷注入反冲

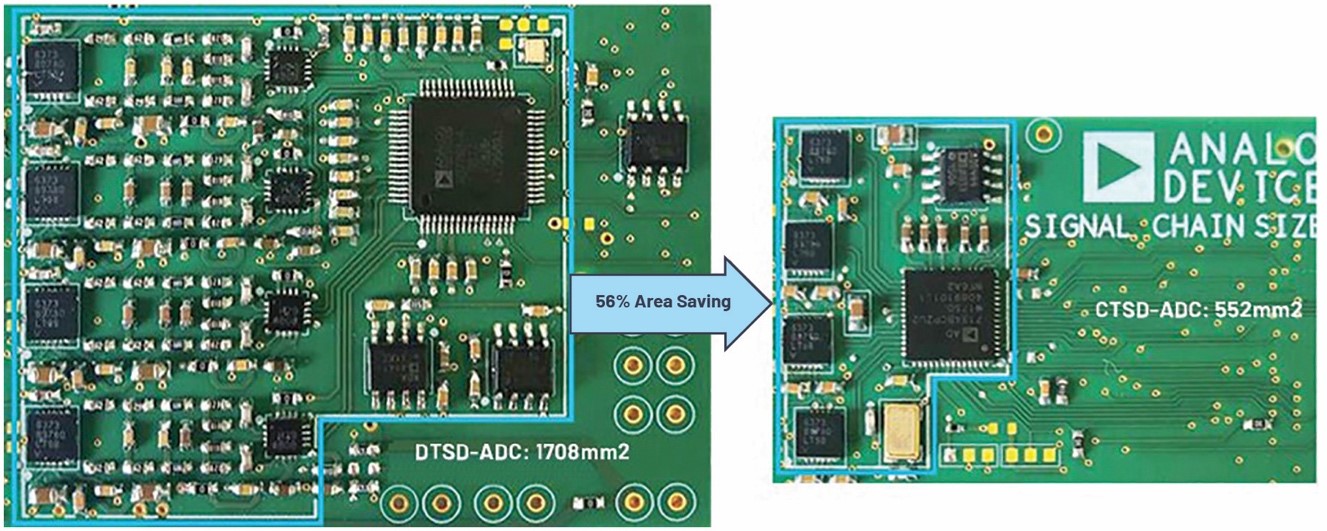

图2 DTSD和CTSD的尺寸对比,显示使用CTSD ADC可以明显减小尺寸

优化设计、降低BOM成本并减小尺寸的一种方法是使用μModule®器件。这些器件是高度集成的解决方案,包含转换器、缓冲器和无源组件。采用这种新型CTSD技术,就可以直接驱动ADC,无需将放大器用作缓冲器。此外,这种新拓扑还可以简化滤波器设计。图1显示传统的离散时间ADC (DT-ADC)和CTSD转换器之间的区别。与传统设计相比,CTSD设计可以将尺寸缩减68%。

在传统的DT-ADC(例如SAR ADC或Σ-Δ ADC)中,会使用开关电容拓扑。ADC和参考输入端就是这种情况。这会使“采样”和“保持”两个阶段之间出现差分。它们分别对应“保持”电容的充电和放电。所以,由于寄生特性(电荷注入反冲),必须提供足够电流,以便进行充电、放电以及电荷吸收。许多传感器无法提供如此高的电流,因此需要进行缓冲。除了此功能之外,驱动器的速度还必须足够快(建立时间短,摆率高),以便解决“采样”阶段(参见图1c)结束时稳定输出,从而避免给目标信号带来更多误差。所以,对ADC驱动器的要求非常高。

CTSD转换器具有阻性输入,可以直接由传感器驱动。如果传感器无法驱动ADC(例如,如果传感器的阻抗非常高),可以插入一个简单的放大器来实现阻抗转换。

CTSD还有一个优势,就是它本身具有抗混叠滤波器(低通滤波器)特性。传统拓扑需要在输入端使用低通滤波器来滤除高频干扰信号。这是因为奈奎斯特准则要求采样速率必须至少为所需信号频率的2倍。如果采样速率过低,可能会出现混叠,导致干扰噪声进入信号。对于CTSD转换器本身的抗混叠滤波器特性,一种解释是:采样不是发生在调制器输入端,而是发生在环路滤波器之后。

结论

CTSD拓扑为优化信号链提供了传统架构之外的另一种新的解决方案。此外,如果非常注重上市时间、BOM或尺寸因素,那么AD4134等ADC产品将会是一个非常不错的选择。它们具有阻性输入且本身自带滤波器属性,可以帮助简化和优化许多设计。在许多应用中,可以无需使用ADC驱动器、滤波器设计中的无源组件和基准电压源缓冲器。《模拟对话》刊登了有关该主题的系列文章,详细阐述了上述优势以及许多其他特性。

作者简介

自2017年4月至今,Benjamin Reiss一直在ADI德国慕尼黑公司工作。他于2016年毕业于埃尔朗根-纽伦堡大学,获得纳米技术硕士学位。完成ADI公司的培训生项目后,他加入区域团队,担任现场应用工程师,为许多客户提供支持。联系方式:benjamin.reiss@analog.com。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码