先进工艺下芯片的胜负手:高效验证

Intel发布了Stratix 10 GX 10M FPGA,这款巨型芯片拥有1020万个逻辑单元,集成了433亿个晶体管。类似的还有AMD发布的二代霄龙芯片,拥有395.4亿个晶体管。这些超大规模的芯片不断刷新着晶体管的数目纪录,在坐拥性能怪兽称号的同时,也将芯片的设计生产难度不断提高。

据统计,28nm的IC设计平均费用为5,130万美元,使用FinFET技术的7nm工艺,则需要2亿9,780万美元,两者差距为6倍。

高昂的设计费用让芯片企业都希望能一次就投片成功,但实际上, 2018 年 ASIC 芯片的一次投片成功率只有 26%。

先进的工艺节点引发了新的问题,如果芯片的验证不能跟上,就会造成反复投片问题,让芯片设计者可能“血本无归”。验证的准确性已经决定着芯片的“生死”。

无处不在的验证

从芯片最初的架构设计到最后的流片,验证工作贯穿了整个设计流程,整个芯片设计70%左右的工作量已经被验证所占据。

庞大的芯片设计规模和指数增长的芯片结构复杂度,无所不在的连接,平台的安全性,在先进工艺的环境下,一颗能完美运行的芯片更需要多层次的反复验证。

从前往后,通常的芯片验证包括了IP核/模块级验证(Block-LevelVerification)、系统级验证(System-Level Verification)、静态时序分析和时序验证(Static timing analysis & Timing Verification)、版图验证(Physical verification)等多个步骤。

版图验证是横亘在流片之前的最后一道验证工序,在所有的检查和验证都准确无误的情况下,芯片设计阶段就告完成,下面将进入晶圆厂进行制造。

作为连接着设计通向生产大门的守门人,版图验证的重要性不言而喻。晶圆厂生产芯片有一定的规则,设计公司设计出来的版图如果不遵守这些规则,就无法从图纸变成真正的芯片。版图验证就是确保芯片要严格遵守这些规则。

这些规则被叫做设计规则(Design Rule), 在版图设计过程中需要不断进行设计规则检查,这个过程叫做DRC(Design Rule Check)。

DRC的主要目标是在设计中实现可靠性并提高芯片的良率。晶圆代工厂提供的所有规则都以验证规则文件的形式作为物理验证工具的输入提供。如果违反任何一项规则,DRC将会反映在设计中。

版图完成之后还要确保功能与原理图中的设计是否一致,有专门的工具进行这一项检查,这项检查流程叫做LVS(Layout Versus Schematic)。

此外,还有电学规则检查ERC(Electrical Rule Check)和针对制造的设计检查DFM(Design For Manufacture)来发现影响制造质量与良率的因素。

如此复杂的检测,如果没有功能强大的设计工具来支持是无法想象的。目前,市面上有多种版图验证工具,“粉丝”最多的就是Mentor公司的Calibre平台。它也是芯片设计中的Golden Signoff(设计签收)工具。

设计与先进工艺间的桥梁

Calibre是Mentor公司专为复杂芯片设计的物理验证挑战而研发的业界最高性能平台。它基于先进的层次化算法和技术,能够快速、准确、完善的对混合集成电路进行物理验证及寄生提取。目前,它已经被全球主流的晶圆厂采用,并成为其内部的物理验证标准。

“该工具持续发展提高,和客户之间形成正反馈,终于稳占市场经久不衰。”一位业内专家这样评价Calibre平台。

主流的晶圆厂在开发工艺的时候,会用Calibre平台去验证工艺实际效果,当验证规则成型以后,再给设计公司使用。如此往复,就在设计公司和晶圆厂之间建立了一座桥梁。

有一个经典案例,Mentor与TSMC携手,在开发12nm和7nm FinFET Plus工艺时,增加了工具的覆盖率,还优化了设计套件的运行速度。此外,TSMC和Mentor还紧密配合,以便双方的共同客户能够了解Calibre设计规则检查(DRC)和多重曝光软件方面的极紫外(EUV)光刻要求。

TSMC是开发先进工艺的领路者,与这样的伙伴合作,Calibre平台积累大量丰富的经验,开发了很多先进功能。在与其他晶圆厂或设计公司合作时,这些功能和经验会帮助其避开不少障碍。

整个Calibre平台包含了很多模块,针对不同的验证目标,最主要的模块如下:

Calibre DRC——作为工作在展平模式下的设计规则检查(DRC)工具,Calibre DRC先展平输入数据库,然后对展平的几何结果进行操作。

Calibre LVS——作为工作在展平模式下的版图与原理图对照(LVS)工具,Calibre LVS先展平输入数据库,然后对展平的几何结果进行操作。

Calibre xRC——全芯片寄生参数提取工具,提供晶体管级、门级和混合级别寄生参数提取的能力,支持多层次的分析和仿真。

Caliber PERC 平台——旨在提高可靠性并保护设计免受静电放电 (ESD) 的影响,该平台可实现全芯片 IO-ESD 和跨电源域 ESD 设计验证。

Calibre YieldEnhance——该工具提供了一种自动化的布局增强方法,可以在不牺牲面积的情况下提高产量。

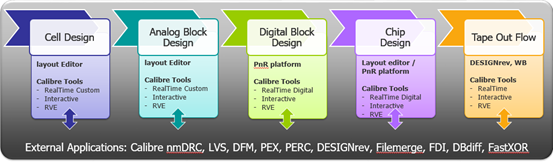

图1 Calibre在芯片设计各环节的应用

芯片设计公司依靠Calibre平台去解决芯片的可靠性问题,同时也提升了生产良率。因为芯片良率与可靠性之间的紧密联系已经得到充分的研究和记录,良率高,可靠性随之也好。但在进入先进工艺节点之后,芯片的良率提升已经十分困难。好在有了Calibre平台等一系列验证工具,让良率提升有了强大的武器。

提升验证效率

芯片都是根据市场需求而生的,而市场需求往往瞬息而变,这就是所谓的“时间窗口”。赶不上时间窗口,芯片就没有前途。对于晶圆厂而言,工艺成功取决于其控制设计制造工艺窗口(design-manufacturing process window)的能力:不仅要能够最大限度扩大工艺窗口,还要能够在尽可能短的时间内预防、发现、评估和修复热点。因此,设计工程师和工艺工程师都对EDA的精度和速度都提出了更高的要求。

“在验证方面,一是要Runtime时间短,验证周期要短;第二是在兼顾速度的时候,Debug要准,而这些都是Calibre的优势。”Mentor的工程师告诉记者。

Calibre还非常容易上手,使用体验类似点工具,对新手非常友好。由于已经成为物理验证方面的标准,其他的设计平台都集成了Calibre工具,设计者一旦掌握就不会受到平台的限制。

最重要的是,Calibre本身集成了晶圆厂先进工艺的精髓,比如其中的Calibre SmartFill规则集就是由Mentor和TSMC为TSMC的N16制程而联合开发。SmartFill可以将版图密度分析和多种填充方案相结合为复杂的数字、模拟芯片提供最佳的填充策略。

需要解释的是,Fill(填充)是一个芯片设计中非常重要的工艺,防止芯片在制造过程中由于曝光过渡或不足而导致的蚀刻失败,金属(metal)是主要的填充物之一。以前,填充是无规律进行的,被称为Dummy metal,容易造成效率低下。针对问题,Mentor发明了SmartFill技术,可以根据工艺的实际情况进行填充,极大提升了效率和芯片可靠性。

值得一提的是,SmartFill集成了ECO填充功能,可确保实现较晚的设计更改并快速高效地重新填充设计,同时将运行时间,填充数据库的大小和时序影响最小化。最为重要的应用实例就是,最初为 20nm 设计而研发的 Calibre YieldEnhancer ECOFill 解决方案现已广泛应用于 TSMC 7nm 到 65nm 范围内的所有工艺节点。各个工艺节点的设计人员能够在更改初始设计时最大限度减少填充运行时间、管理分层填充以及尽可能地减少形状移除的情况。

图2 Calibre良率提升与可靠性提高版图解决方案

版图验证是道复杂的工序,初学者掌握起来还是有一定困难的。好消息是,最近Mentor公司专门开设了一系列在线讲座,讲授Calibre的使用方法和版图验证方法。

2020年5月19日,最新一期讲座将介绍Calibre YE的多种填充解决方案。针对普通的金属填充,主要介绍如何使用最佳实践方法优化操作流程。还将介绍多种个性化的填充方案,主要包括Net感知的填充方案、ECO填充方案、PowerVia填充方案,以及如何使用YE添加Filler Cell。

关键词: 芯片

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码