整合ARM、FPGA与可编程模拟电路的单芯片方案

如果世上真的有典型或者通用的嵌入式系统应用,主流半导体公司的产品目录一定会薄很多。现在设计人员不仅要从多种处理器架构中进行选择(大多数嵌入式系统设计都以处理器内核为中心),而且外设、通信端口和模拟功能组合的选择几乎无限。而这正好指出了嵌入式应用的多样性所带来的问题:尽管有如此多的标准端口可供选择,却很少有设计人员能够最终实现单芯片解决方案。他们的选择往往都是微控制器加大量辅助芯片,其中常常包括一些用以提供微控制器所缺乏的特定逻辑功能的可编程逻辑,和作为实际信号接口的模拟 IC。

设计人员极少实现单芯片解决方案,原因之一在于他们只能在有限的预定义功能组合中作出选择。其它原因还包括应对设计变化的灵活性:功能与初始规格的匹配越精确,往后在项目进展过程中能够适应不断变化的要求的空间就越小。然而,一旦解决方案要采用多芯片来实现,设计安全性的问题就凸显出来了。由于芯片间布线板级暴露,而且MCU代码和/或FPGA配置数据没有加密,整个设计便很容易被盗版。

而随着Actel SmartFusion器件的推出,设计人员现在可以使用单芯片解决方案来提供期盼已久的可编程逻辑、可编程模拟电路与一个功能强大的业界领先32位架构微控制器内核的结合。最重要的是,有一个同样全面的工具链支持该器件的广泛灵活性(模拟和数字功能均可定制)与ARM Cortex-M3处理器的软件可编程性相结合。

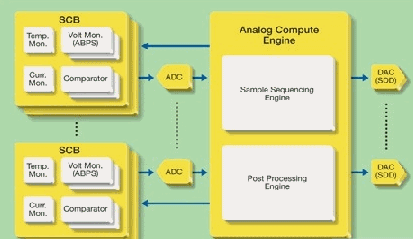

F2: SmartFusion中的可编程模拟模块(包括:精度为1%的ADC和DAC、多达3个采样频率为600 Ksps的12位ADC、最多三个12位第一阶sigma delta DAC、 最多10个50 ns高速比较器以及集成多种温度、电压和电流监控功能。)

爱特(Actel)公司在非易失性闪存工艺方面的战略性投资,带来了是三项截然不同的技术的整合。其优势相当明显:快闪编程器件把它的可编程逻辑配置数据和微控制器程序代码永久性存储在片上,因此它能上电即用,而不必等待从邻近的EEPROM 装载配置数据。而这也大大有助于解决知识产权(IP)安全性问题,因为配置数据不再因器件间的传送而暴露,从而避免被中途截取或被盗。更进一步的保护是出厂保护,即闪存一旦被编程就会被永久性锁定以防止被读取,这就是Actel器件上的FlashLock功能。此外,由于基于快闪的IC可对小批量器件进行编程,或是在制造过程的最后期在系统内对器件编程,故而适合众多中小型生产规模的典型嵌入式设计。

这种硅工艺技术还有其它的优点。相比纯逻辑CMOS工艺,快闪需要高电压来编程和擦除,故内置有高模拟电压电平的监控能力。爱特采用的工艺可实现片上模块间的隔离(通过一种三阱结构),允许模拟和数字模块并排放置,却又彼此互不干扰。尽管这是一个混合信号环境,模拟功能仍能够保持出色的偏移和噪声等参数规格。

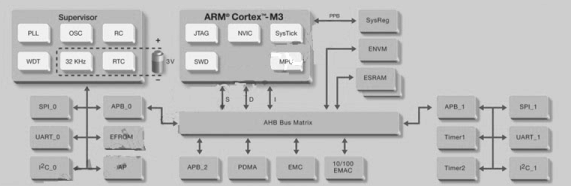

F3: 微控制器子系统

在模拟能力方面,SmartFusion器件带有多达3个12位逐次逼近(SAR) 模数转换器(ADC),支持全分辨率500 Ksps工作。其中每个ADC都有一个对应的第一阶1位sigma-delta 数模转换器(DAC),而且具有500 Ksps的更新速度和高效的12位分辨率。它还有一个新的可编程元件,就是信号调节模块(SCB)。SCB由精确的高压.、电流.、温度.以及高速(50 ns)比较器组成。高压.,亦即有源双极型预定标调节器(ABPS),能够提供从-11.5V到+14V的电压监控能力。专门设计的电流.通过放大外接低阻值感测电阻上的电压降来实现检测电流;而温度.则通过外接二极管来实现检测温度。

所有这些模拟功能性在功能性配置和参数值方面都是完全可编程的,并拥有一个基于图形用户界面(GUI)的软件环境,以及众多用于板上FPGA配置的设计工具。

SmartFusion器件包含有多达500k可编程逻辑门电路,与基于快闪的 ProASIC3 FPGA器件系列一样。这个逻辑电路支持350 MHz的系统性能,内置容量高达108 Kb的 SRAM,并拥有大量工作频率高至350 MHz的数字I/O,支持LVDS、LVPECL、PCI/PCI-X等接口标准,可驱动高达24mA的电流。设计选择包括爱特的HDL(硬件描述语言)工具链、Libero集成设计环境,可以硬件创建逻辑功能,或者是在GUI以拖放式(drag-and-drop)操作创建设计。这种方法可快速输入预定义的IP模块,这些模块可能是源于以前设计的复用元件,或者是爱特提供的函数库内的函数,也可能是第三方供应商提供的IP。

这些芯片上除了一个基于ARM Cortex-M3的微控制器子系统之外,还有众多完全可配置逻辑和模拟功能。

相比分立IC,逻辑和线性模块能够提供不折不扣的高性能,同样地,ARM Cortex-M3处理器也是一种全功能全规格的实现方案。它是一种已获全面集成的功能性模块——是一个“硬”核,而不是在FPGA逻辑部件上编程的“软”版本。系统运行时钟频率高至100 MHz,性能可达 125 DMIPS,并带512 KB 的闪存和64 KB 的 SRAM。它的功能强大,足以运行复杂的算法,比如精度电机控制,或者甚至好几个电机的多轴控制。另外,在系统管理应用中,它能够管理电压监控、定序(sequencing)、风扇控制及相关“系统内务管理”等多项任务,同时仍有充足的容量来运行更高的用户应用级任务。作为一个全功能的ARM Cortex-M3设计,它还带有一系列外设,包括10/100 以太网 MAC 和其它接口,比如SPI、I2C和UART等。混合信号I/O 线运行频率高达180 MHz,可驱动6 mA的电流。其它微控制器工程人员常用的功能还包括实时时钟、看门狗定时器、8路DMA控制器和外部存储控制器(用于额外的代码或数据的存储)。为了最大效率地使用硅面积,这套外设也是“硬连线的”,但设计人员能够通过使用邻近的可编程逻辑来对之进行扩展和调整。ARM Cortex-M3 处理器经由相同的5层AHB 总线矩阵结构与FPGA 结构紧密连接,片上外设连接性能带宽高达16 Gbps。

如上所述,SmartFusion架构的处理能力显而易见。此外,SmartFusion架构的灵活性优势还体现在以下事实中:许多前端处理任务根本不需要调用ARM Cortex-M3处理器。与其它片上元件一样,模拟计算引擎(ACE)也是一个全新的概念。ACE是一个半自治模块,可在无需ARM Cortex-M3处理器干预下执行扩展模拟预处理和后处理任务,比如信号采集的采样和排序。

这个新的器件系列可为嵌入式系统设计人员提供真正的单芯片工具,其在硬件方面完全可配置,软件方面完全可编程,并充分利用了ARM架构能够支配的所有代码设计资源。这些芯片还附带有一整套工具,可以为软件代码编写人员、模拟接口设计人员和RTL编程人员等提供一个熟悉的环境,而且能够在这些技术人员向完整的FPGA、ARM和模拟领域拓展时予以他们支持。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码