模数转换器时钟优化:测试工程观点

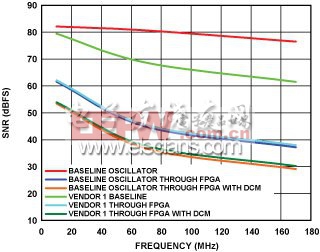

SNR,绿色曲线示出了在相同的时钟下,使用FPGA作为高性能振荡器和转换器之间的门驱动器时获得的性能与基线性能之间的差异。在40 MHz下,FPGA将SNR减少到52 dB(8.7 bit性能),而DCM贡献了额外8 dB(1.3 bit)的SNR下降。SNR下降29 dB的性能差异是非常令人担忧的,在使用式1计算时,意味着FPGA驱动器门自身即可带来约10 ps的抖动。

图18. FPGA门驱动电路影响AD9446-80的性能

选择最佳的时钟驱动器是困难的。表2给出了市售的多个驱动器门所增加抖动的大致比较结果。表格下方给出的建议有助于获得优良的ADC性能。

表2. 时钟驱动器门及其增加的抖动

| 逻辑系列 | 注释 |

FPGA | 33 ps~50 ps(仅包括驱动器门,未包括DLL/PLL内部的门)1 |

74LS00 | 4.94 ps2 |

74HCT00 | 2.2 ps2 |

74ACT00 | 0.99 ps2 |

MC100EL16 PECL | 0.7 ps2 |

AD951x系列 | 0.22 ps2 |

NBSG16,ECL摆幅减少(0.4V) | 0.2 ps2 |

ADCLK9xx,ECL时钟驱动器系列 | 0.1 ps2 |

1制造商的说明书

2基于ADC SNR的下降换算的值

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码